Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: UFSM

Orgão: UFSM

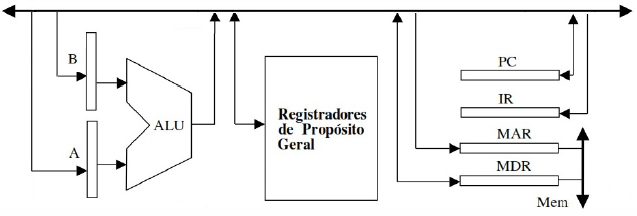

A figura a seguir representa a via de dados de um processador com um barramento interno.

Além do barramento, a via de dados é composta por: um conjunto de registradores de propósito geral, contador de programa (PC), registrador de instrução (IR), uma unidade lógica e aritmética (ALU) com um registrador em cada uma das suas entradas (A e B), além do par formado pelo registrador de endereçamento de memória (MAR) e pelo registrador de dados temporários da memória (MDR), que se conectam ao barramento de memória (Mem).

Considere que a próxima instrução de um programa que está sendo executado pelo processador é uma instrução de soma do tipo

Add R1, R2, R0.

Essa instrução ocupa 4 bytes de memória e determina que os conteúdos de R1 e R2 são somados e o resultado armazenado em R0.

A seguir, a 2ª coluna apresenta todas as micro-operações necessárias para o tratamento dessa instrução, desde a sua busca até o armazenamento do resultado em R0. Como a via de dados permite que algumas dessas microoperações sejam feitas em paralelo, o ciclo da instrução necessita de apenas 6 subciclos, identificados na 1ª coluna.

Numere os parênteses da 2ª coluna, associando cada micro-operação ao subciclo no qual ela será realizada.

| 1ª Coluna | 2ª Coluna |

| 1. Primeiro subciclo | ( ) MDR !$ \leftarrow !$ Mem[MAR] |

| 2. Segundo subciclo | ( ) A !$ \leftarrow !$ (PC) |

| 3. Terceiro subciclo | ( ) PC !$ \leftarrow !$ (A)+4 |

| 4. Quarto subciclo | ( ) IR !$ \leftarrow !$ (MDR) |

| 5. Quinto subciclo | ( ) B !$ \leftarrow !$ (R2) |

| 6. Sexto subciclo | ( ) MAR !$ \leftarrow !$ (PC) |

| ( ) A !$ \leftarrow !$ (R1) | |

| ( ) R0 !$ \leftarrow !$ (A) + (B) |

A sequência correta é