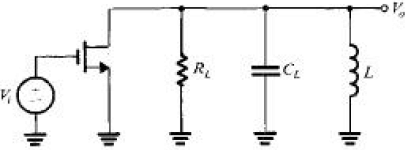

Deseja-se projetar um amplificador sintonizado conforme o circuito abaixo, tendo f0 = 1/!$ \pi !$ MHz, faixa de passagem de 3 dB igual a 10/!$ \pi !$ kHz e ganho de frequência central de -25. O FET (Field Effect Transistor – Transistor de Efeito de Campo) disponível no ponto de polarização tem transcondutância, gm, igual a 5 mA/V e resistência de saída, ro, igual a 10 kΩ. A capacitância da saída é desprezível. Os valores de RL, CL e L são, respectivamente:

Provas

Questão presente nas seguintes provas