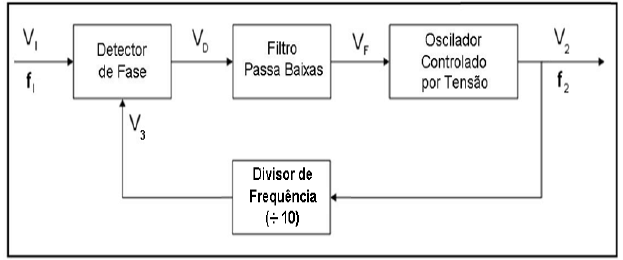

Um circuito muito utilizado em eletrônica é a malha de captura de fase (PLL, do inglês Phase-Locked Loop), composto por um detector de fase, um filtro passa baixas e um oscilador controlado por tensão (VCO). Na figura abaixo, apresenta-se o diagrama em blocos de um circuito PLL, em cuja malha de realimentação foi incluído um divisor de frequência que, nessa aplicação, divide a frequência por 10.

Considerando uma operação em regime permanente e que a frequência do sinal periódico de entrada (V1) é de 2 kHz, a frequência do sinal na saída do VCO (V2) será