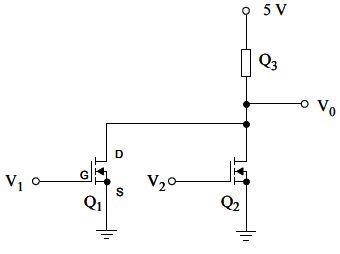

O circuito digital ilustrado acima é constituído por dois transistores NMOS do tipo enriquecimento (Q1 e Q2), idênticos, e por um transistor NMOS do tipo depleção (Q3), que desempenha a função de resistor não linear. O circuito é projetado para trabalhar com dois níveis de tensão de entrada: 0,2 V (nível lógico 0) e 4,0 V (nível lógico 1). Quando Q1 é alimentado com 4,0 V, a corrente de dreno e a potência estática dissipada correspondentes são 555 :A e 166,5 :W, respectivamente. Com base nessas informações, e sabendo-se que a tensão de limiar de Q1 é dada por Vt = 2,0 V, julgue o próximo item.

O circuito acima implementa uma porta lógica do tipo NOR (não-ou), e os níveis de tensão de saída (V0) são indicados na tabela verdade a seguir.

| ENTRADA | SAÍDA | ||||

|

V1 |

V2 | V0 | |||

|

nível de |

nível lógico |

nível de tensão [V] |

nível lógico |

nível de tensão [V] |

nível |

| 0,2 | 0 | 0,2 | 0 | 5,0 | 1 |

| 0,2 | 0 | 4,0 | 1 | 0,1 | 0 |

| 4,0 | 1 | 0,2 | 0 | 0,1 | 0 |

| 4,0 | 1 | 4,0 | 1 | 0,1 | 0 |