Foram encontradas 110 questões.

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: DECEx

Orgão: EsFCEx

Uma CPU tem uma unidade aritmética que adiciona bytes e então ajusta os bits de flag V, C e Z como segue. O bit V é definido como 1 (ligado) se ocorrer overflow aritmético (em aritmética de complemento de 2). O bit C é ligado se é gerado um carry-out (vai um) do bit mais significativo durante a operação. O bit Z é ligado se o resultado for zero. Quais são os valores dos flags V, C e Z após a adição dos bytes de 8 bits 11001100 e 10001111?

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: DECEx

Orgão: EsFCEx

De acordo com o padrão IEEE, um número de ponto flutuante de precisão simples N é definido como

!$ N = (-1)^S x 1.F x 2^{E-127} !$

onde S é o bit de sinal, F é a mantissa fracionária e E o expoente polarizado. Um número de ponto flutuante é armazenado como S:E:F, onde S, E e F são armazenados em 1 bit, 8 bits e 23 bits, respectivamente. Qual é o valor decimal do número de ponto flutuante C1E00000 (notação hexadecimal)?

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: DECEx

Orgão: EsFCEx

Em um computador RISC com pipeline onde todas as instruções aritméticas têm o mesmo CPI (ciclos por instrução), analise as ações abaixo que melhorariam o tempo de execução de um programa típico e, a seguir, assinale a alternativa correta.

I. Incrementar a taxa do ciclo do relógio.

II. Proibir qualquer forwarding no pipeline.

III. Dobrar o tamanho da cache de instruções e da cache de dados sem mudar o tempo de ciclo do relógio.

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: DECEx

Orgão: EsFCEx

Suponha que um certo produto de software tem um tempo médio entre falhas (MTBF) de 10.000 horas e um tempo médio para reparar (MTTR) de 20 horas. Se o produto é utilizado por 100 clientes, qual é a sua disponibilidade?

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: DECEx

Orgão: EsFCEx

Dois processadores, M-5 e M-7, implementam o mesmo conjunto de instruções. O processador M-5 usa um pipeline de 5 estágios e um ciclo de relógio de 10 nanosegundos. O processador M-7 usa um pipeline de 7 estágios e um ciclo de relógio de 7,5 nanosegundos. Analise as afirmativas e, a seguir, assinale a alternativa correta.

I. O pipeline do M-7 tem um desempenho máximo melhor do que o pipeline do M-5.

II. A latência de uma instrução é menor no pipeline do M-7 do que no do M-5.

III. Programa executando no M-7 sempre “rodará” mais rápido do que executando no M-5.

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: DECEx

Orgão: EsFCEx

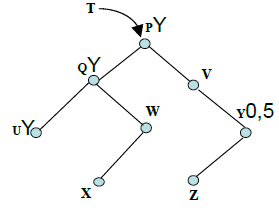

Dada a árvore binária T abaixo,

qual das seguintes opções representa um caminhamento postorder em T?

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: DECEx

Orgão: EsFCEx

Os computadores digitais utilizam métodos para representar números inteiros. Um dos métodos utilizados é a representação em complemento de 1, onde o bit mais a esquerda representa o sinal do número, onde 0 corresponde ao sinal + e o 1 o sinal -. Qual a principal anomalia apresentada por este método de representação de números inteiros?

Provas

Qual o padrão de projeto que representa uma operação a ser executada nos elementos de uma estrutura de objetos, permitindo inclusive que uma nova operação seja definida sem mudança nas classes dos elementos sobre os quais opera?

Provas

Qual o padrão de projeto que fornece um substituto ou marcador da localização de outro objeto para controlar o acesso ao mesmo?

Provas

Considerando a classe Orange em linguagem Java,

class Orange {

public static void main(String args[]) {

String a = "A";

String b = "B";

String c = "AB";

System.out.print((("A"+"B")=="AB") + ",");

System.out.print(("A"+"B")==c);

}

}

assinale a alternativa que descreve corretamente o que vai ser mostrado quando esta classe for compilada e executada.

Provas

Caderno Container