Foram encontradas 100 questões.

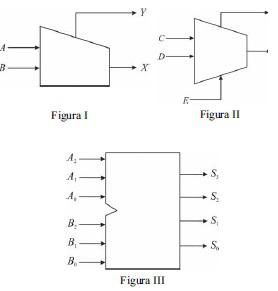

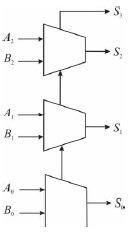

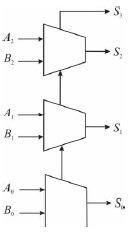

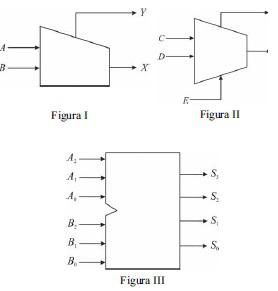

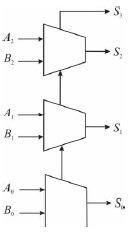

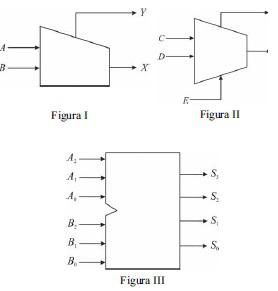

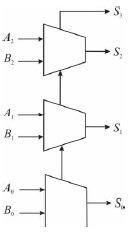

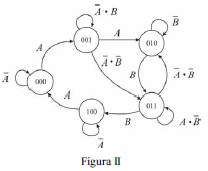

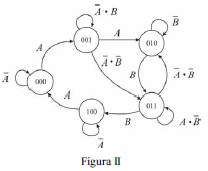

O sistema lógico mostrado na figura III acima é um somador de palavras de 3 bits, isto é, a palavra binária representa a soma das palavras binárias e , em que o subscrito 0 denota o bit menos significativo. Para executar esta tarefa de somador, o sistema na figura III é construído usando os sistemas nas figuras I e II, como mostrado a seguir:

Considerando as informações e as figuras acima, julgue os itens que se seguem.

Provas

itens a seguir.

Provas

O sistema lógico mostrado na figura III acima é um somador de palavras de 3 bits, isto é, a palavra binária representa a soma das palavras binárias e , em que o subscrito 0 denota o bit menos significativo. Para executar esta tarefa de somador, o sistema na figura III é construído usando os sistemas nas figuras I e II, como mostrado a seguir:

Considerando as informações e as figuras acima, julgue os itens que se seguem.

Considerando as informações e as figuras acima, julgue os itens que se seguem.

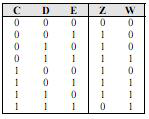

É correto afirmar que W = C. D + C.E + D.E..

Provas

O sistema lógico mostrado na figura III acima é um somador de palavras de 3 bits, isto é, a palavra binária representa a soma das palavras binárias e , em que o subscrito 0 denota o bit menos significativo. Para executar esta tarefa de somador, o sistema na figura III é construído usando os sistemas nas figuras I e II, como mostrado a seguir:

Considerando as informações e as figuras acima, julgue os itens que se seguem.

Considerando as informações e as figuras acima, julgue os itens que se seguem.

Se C=A,D= B e E = 0, Então W=Y e Z =XProvas

O sistema lógico mostrado na figura III acima é um somador de palavras de 3 bits, isto é, a palavra binária representa a soma das palavras binárias e , em que o subscrito 0 denota o bit menos significativo. Para executar esta tarefa de somador, o sistema na figura III é construído usando os sistemas nas figuras I e II, como mostrado a seguir:

Considerando as informações e as figuras acima, julgue os itens que se seguem.

Provas

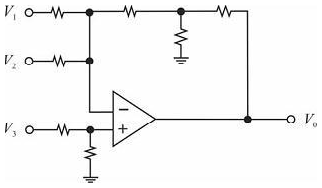

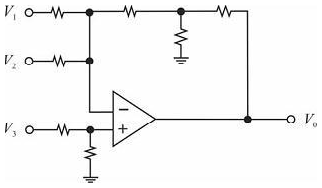

Com base no circuito acima, no qual o amplificador operacional é ideal e todos os resistores são de

Provas

Com base no circuito acima, no qual o amplificador operacional é ideal e todos os resistores são de

Provas

Com base no circuito acima, no qual o amplificador operacional é ideal e todos os resistores são de

Provas

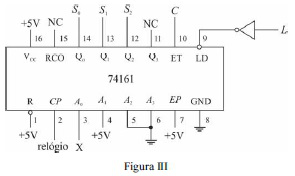

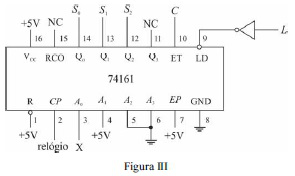

Considere que a máquina de estados mostrada na figura II tenha sido corretamente implementada usando um chip 74161, da forma apresentada na figura III. No circuito da figura III, S2S1S0 representa o estado atual da máquina de estados e NC indica um pino não conectado.

Provas

Considere que a máquina de estados mostrada na figura II tenha sido corretamente implementada usando um chip 74161, da forma apresentada na figura III. No circuito da figura III, S2S1S0 representa o estado atual da máquina de estados e NC indica um pino não conectado.

Provas

Caderno Container