Foram encontradas 439 questões.

Considere um processador em cujo conjunto de instruções há diferentes modos de endereçamento. Neste processador podem ser executadas as instruções em assembly listadas abaixo.

I. MOV A, #100 ; Carrega 100 no acumulador.

II. MOV A, 20 ; Transfere para o acumulador o conteúdo do endereço 20 da RAM Interna.

III. MOV A, @R0 ; Coloca no acumulador o conteúdo do endereço que está em R0.

IV. MOV A, R0 ; Coloca no acumulador o conteúdo de R0.

Os tipos de endereçamento utilizados nas instruções de I a IV são, correta e respectivamente,

Provas

- Fundamentos de ProgramaçãoAlgoritmosFatorial e Fibonacci

- Fundamentos de ProgramaçãoAnálise Assintótica (Notação Big-O)

- Fundamentos de ProgramaçãoComplexidade

Considere o algoritmo abaixo.

static int fibonacci(int n) {

if (n <= 1) {

return n;

}

return fibonacci(n - 2) + fibonacci(n - 1);

}

A complexidade deste algoritmo, na notação Big O, é

Provas

- Fundamentos de ProgramaçãoAlgoritmosAlgoritmos de OrdenaçãoQuick Sort

- Fundamentos de ProgramaçãoAlgoritmosDividir e Conquistar

- Fundamentos de ProgramaçãoComplexidade

Provas

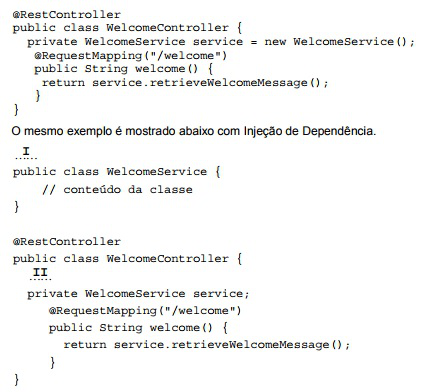

Considere a classe abaixo em uma aplicação Java que utiliza o Spring Framework, sem o uso de Injeção de Dependência.

Provas

Considere o fragmento de código PHP abaixo.

<?php

$processos = array("Processo 1", "Processo 2", "Processo 3", "Processo 4");

($processos, "Processo 5");

($processos, "Processo 5");

($processos);

($processos);

?>

Se o array $processos for tratado como pilha, para adicionar um elemento no topo da pilha e depois removê-lo utilizam-se nas lacunas I e II, respectivamente, os comandos

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FCC

Orgão: TRF-5

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FCC

Orgão: TRF-5

A typical computer system provides a hierarchy of different types of memories for data storage. Consider the statements below.

I. The hard drive has a local data cache. Because the hard drive access speed is so much slower, disk access are normally done asynchronously at the hardware level. The hard drive controller will acknowledge the instruction right away, and will take sometime to populate the disk cache with the requested data block, and then, at a later time, raise an interrupt to notify the interested party that the data access is complete. This model of interrupt based data transfer is asynchronous.

II. The cache is made up of small chunks of mirrored main memory. The size of these chunks is called the line size, and is typically something like 32 or 64 bytes. The cache can load and store memory in sizes a multiple of a cache line. Caches have their own hierarchy, commonly termed L1, L2 and L3. L1 cache is the fastest and smallest; L2 is bigger and slower, and L3 more so.

III. Internal register in a CPU is used for holding variables and temporary results. Internal registers have a very small storage; however they can be accessed instantly. Accessing data from the internal register is the fastest way to access memory. Most registers are implemented as an array of DRAM cells. DRAM is a type of RAM that is much faster and more reliable than the SRAM, which is used for main memory because of its lower cost and smaller space consumption. DRAM does not need to be electrically refreshed as does SRAM.

The correct statement (s)

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FCC

Orgão: TRF-5

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FCC

Orgão: TRF-5

Dentre as operações de aritmética computacional em binário e hexadecimal há a multiplicação e a divisão pela base. Uma operação deste tipo cujo resultado está corretamente calculado é:

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FCC

Orgão: TRF-5

Provas

Caderno Container