Foram encontradas 50 questões.

- Protocolos e ServiçosAcesso Remoto e TerminalSSH: Secure Shell

- Protocolos e ServiçosInternet e EmailHTTP: Hyper Text Transfer Protocol

- TCP/IPUDP: User Datagram Protocol

Observe o seguinte fragmento de datagrama UDP.

0000000000010110 | 0000000001010000 | 0000000000001100 | 0000000001001110 | 0111010010....... |

Considerando a estrutura de um datagrama UDP e a associação entre o número de portas e serviços, é correto afirmar que os serviços de origem e destino do datagrama são

Provas

- Equipamentos de RedeSwitch

- Transmissão de DadosMeios de TransmissãoCabeamento FìsicoCabeamento Estruturado

- Transmissão de DadosPadrões IEEE 802IEEE 802.3: Ethernet

O setor de redes de computadores solicitou a confecção de um cabo de rede do tipo par trançado (categoria 5e) para ligação de dois switches, usando um conector RJ-45 e o padrão de fiação T568A. O fio Branco com Verde e o fio Azul devem ser ligados, respectivamente, nos pinos

Provas

Para estruturar a transmissão de dados em redes Ethernet, a camada de acesso ao meio (MAC, IEEE 802.3) deve gerar um quadro Ethernet que contém diversas informações, divididas em campos. Para garantir que o campo de dados tenha o mínimo de 46 bytes de tamanho, utilizamos o campo

Provas

- Transmissão de DadosCaracterísticas de TransmissãoCodificação e Detecção de Erros

- Transmissão de DadosComutação de Células, Circuitos e Pacotes

Os dados transmitidos, em uma rede orientada à conexão, são encapsulados em pacotes. Quando um pacote é enviado de um transmissor para um receptor, este último realiza um processo de verificação para analisar se o pacote que está sendo recebido foi corrompido ou não. Esse processo de verificação é realizado mediante a análise do

Provas

Sobre as placas-mães, afirma-se:

I | ATX e ITY são formatos de placas mães introduzidos no final da década de 1990. |

II | A CMOS é uma pequena memória volátil que guarda os dados do setup. |

III | MCA, EISA e VLBX foram padrões de barramentos de expansão muito usados em placas mães. |

IV | A temperatura no gabinete interfere na vida útil dos capacitores eletrolíticos em placas-mães que usam esses componentes. |

Dentre as afirmações, estão corretas

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: UFRN

Orgão: UFERSA

Sobre os discos rígidos, afirma-se:

I | O full stroke seek time indica o tempo que a cabeça de leitura demora para se deslocar da primeira até a última trilha do HD. |

II | O tempo de latência médio de HD de 7200 RPM é de 1,38 ms. |

III | O tempo de acesso de um HD é calculado dividindo-se 60 pela velocidade de rotação e multiplicando-se esse resultado por 1000. |

IV | O tempo de busca track-to-track é o tempo que a cabeça leva para mudar de uma trilha para a sequente. |

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: UFRN

Orgão: UFERSA

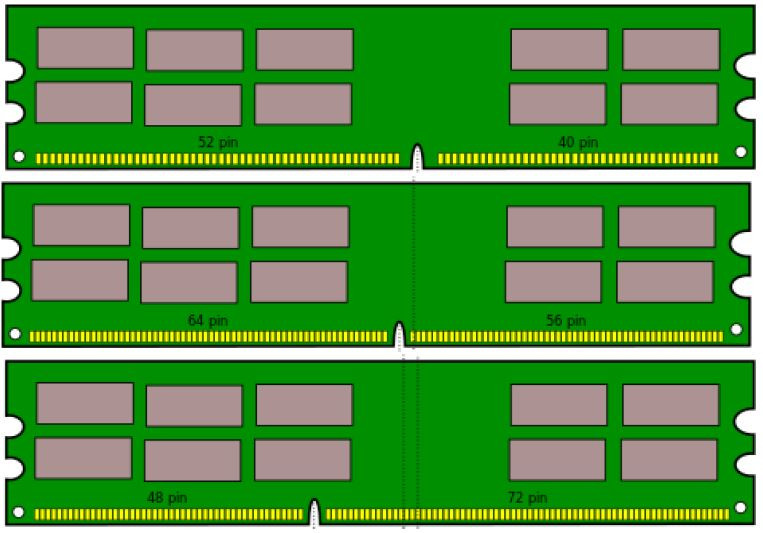

As memórias de taxa dupla de transferência - DDR estão em sua terceira geração comercial e são identificáveis pela ranhura que divide os pinos dos contatos em duas partes. A figura a seguir mostra uma sequência dessas memórias.

Disponível em:<http://upload.wikimedia.org/wikipedia/commons/1/15/DDR_Memory_Comparison.svg> Acesso em: 30 out. 2013.

.

Na ordem de cima para baixo em que essas memórias aparecem na figura, elas são identificadas, respectivamente, como

Provas

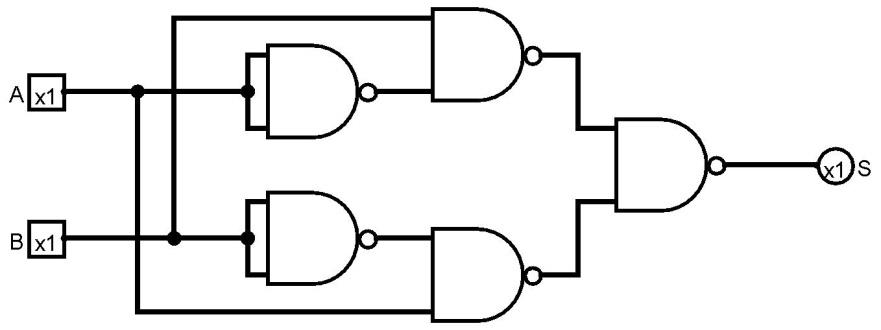

Analise o circuito combinacional a seguir.

Considerando as entradas A e B e a saída S, ele é equivalente, em funcionalidade, a apenas uma porta lógica que opera sobre as entradas A e B gerando S. Essa porta lógica é uma

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: UFRN

Orgão: UFERSA

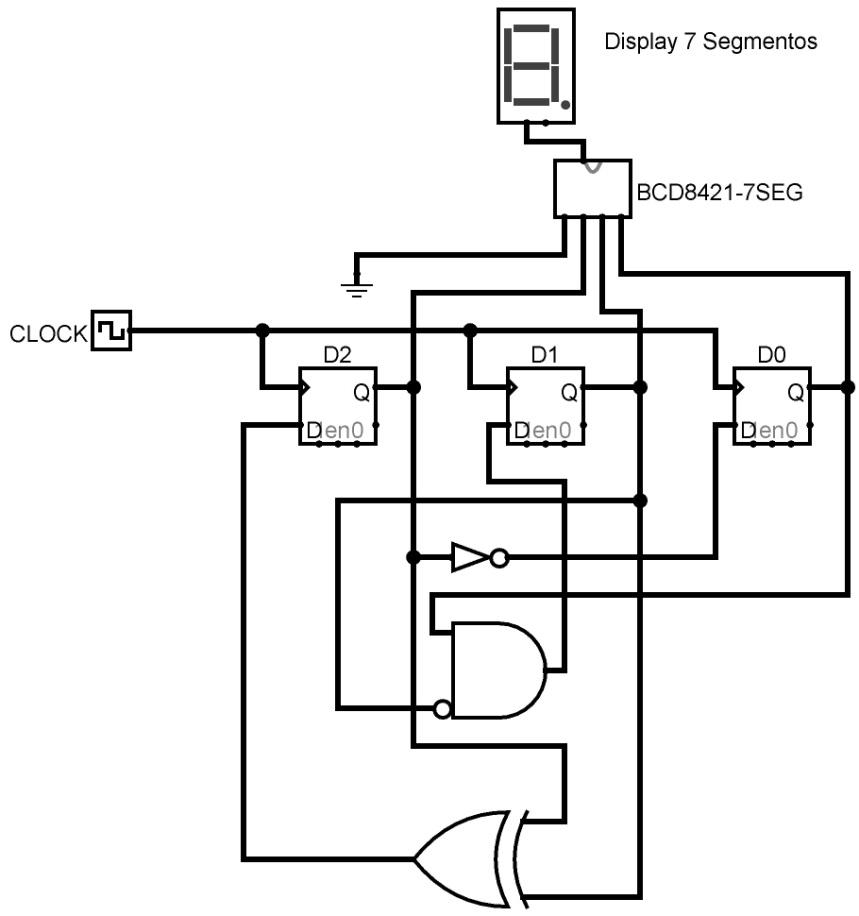

Analise o circuito a seguir.

O circuito combinacional rotulado BCD8421-7SEG é o responsável por converter o número binário formado pelos bits armazenados em D2, D1 e D0 (bit menos significativo) em um conjunto de sinais que alimentam um display de 7 segmentos que mostra o valor decimal correspondente. Considerando o valor inicial mostrado no display de 7 segmentos como 0 (zero), os 10 primeiros algarismos decimais que serão mostrados no display serão

Provas

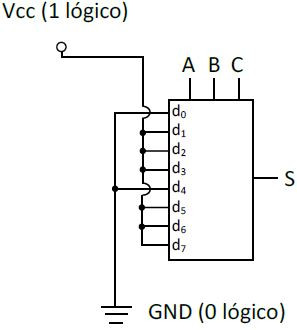

Um multiplexador é um componente digital presente em circuitos modernos para prototipagem de sistemas digitais eletrônicos. Neles, esse componente é usado para implementar funções lógicas. A figura a seguir mostra um diagrama esquemático de tal situação e a tabela verdade de funcionamento do multiplexador.

A | B | C | S0 |

0 | 0 | 0 | d0 |

0 | 0 | 1 | d1 |

0 | 1 | 0 | d2 |

0 | 1 | 1 | d3 |

1 | 0 | 0 | d4 |

1 | 0 | 1 | d5 |

1 | 1 | 0 | d6 |

1 | 1 | 1 | d7 |

A expressão lógica para gerar essa configuração é

Provas

Caderno Container