Foram encontradas 12.703 questões.

889575

Ano: 2011

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: CESGRANRIO

Orgão: Petrobrás

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: CESGRANRIO

Orgão: Petrobrás

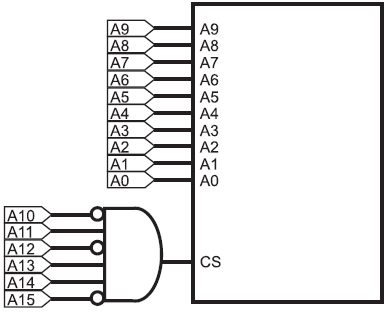

A faixa de endereços mapeada pela memória acima é

Provas

Questão presente nas seguintes provas

889574

Ano: 2011

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: CESGRANRIO

Orgão: Petrobrás

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: CESGRANRIO

Orgão: Petrobrás

A instrução da arquitetura x86 que realiza um acesso direto entre memória e I/O, não passando o dado, portanto, pela CPU, é

Provas

Questão presente nas seguintes provas

872209

Ano: 2011

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: CESPE / CEBRASPE

Orgão: BRB

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: CESPE / CEBRASPE

Orgão: BRB

Provas:

Com relação aos conceitos de arquitetura de computadores, julgue

os itens a seguir.

O barramento USB (universal serial bus) permite a conexão de muitos periféricos simultaneamente ao barramento. Tal barramento está ligado à placa-mãe por uma única conexão.os itens a seguir.

Provas

Questão presente nas seguintes provas

872208

Ano: 2011

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: CESPE / CEBRASPE

Orgão: BRB

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: CESPE / CEBRASPE

Orgão: BRB

Provas:

Com relação aos conceitos de arquitetura de computadores, julgue

os itens a seguir.

O número de bits de um computador — por exemplo, uma máquina de 32 bits — representa o tamanho da célula de memória desse computador.os itens a seguir.

Provas

Questão presente nas seguintes provas

872207

Ano: 2011

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: CESPE / CEBRASPE

Orgão: BRB

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: CESPE / CEBRASPE

Orgão: BRB

Provas:

Com relação aos conceitos de arquitetura de computadores, julgue

os itens a seguir.

Geralmente, as máquinas CISC utilizam os registradores da CPU para o armazenamento dos parâmetros e das variáveis em chamadas de rotinas e funções.os itens a seguir.

Provas

Questão presente nas seguintes provas

832250

Ano: 2011

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: CESGRANRIO

Orgão: Transpetro

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: CESGRANRIO

Orgão: Transpetro

Provas:

O relógio de um processador consiste em um dispositivo que tem como finalidade sincronizar e cadenciar (controlar a velocidade) as ações executadas por essa unidade. Em cada ciclo (intervalo de tempo entre o início da subida/ descida de um pulso até o início de sua descida/subida), uma ação é realizada pelo processador.

Se o intervalo de tempo entre duas ações consecutivas de um processador é igual a 2 nanossegundos, qual será a sua frequência em Gigahertz (GHz)?

Se o intervalo de tempo entre duas ações consecutivas de um processador é igual a 2 nanossegundos, qual será a sua frequência em Gigahertz (GHz)?

Provas

Questão presente nas seguintes provas

832248

Ano: 2011

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: CESGRANRIO

Orgão: Transpetro

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: CESGRANRIO

Orgão: Transpetro

Provas:

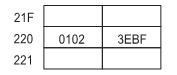

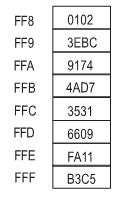

Considere o cenário descrito abaixo, para responder

às questões de nos

34 e 35.

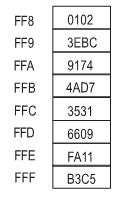

Segue-se o trecho final de uma memória principal, onde

o endereço FFF representa a maior posição endereçável.

Todos os números são apresentados em hexadecimal.

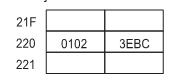

Considere agora um trecho de uma memória cache interligada à memória principal apresentada. Cada linha abriga um bloco de memória com duas células. No exemplo ilustrado a seguir, a linha 220 armazena o bloco que contém as células de endereços FF8 e FF9.às questões de nos

34 e 35.

Segue-se o trecho final de uma memória principal, onde

o endereço FFF representa a maior posição endereçável.

Todos os números são apresentados em hexadecimal.

O processador então envia uma solicitação de escrita à memória principal na célula FF9. Após a operação ser completada, a memória cache tem o valor alterado para 3EBF, mas a memória principal mantém armazenado o valor anterior, que é 3EBC.

Considerando-se esse cenário, tem-se que a memória cache implementa a

Provas

Questão presente nas seguintes provas

832247

Ano: 2011

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: CESGRANRIO

Orgão: Transpetro

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: CESGRANRIO

Orgão: Transpetro

Provas:

Considere o cenário descrito abaixo, para responder

às questões de nos

34 e 35.

Segue-se o trecho final de uma memória principal, onde

o endereço FFF representa a maior posição endereçável.

Todos os números são apresentados em hexadecimal.

O número máximo de células que essa memória pode conter será igual aàs questões de nos

34 e 35.

Segue-se o trecho final de uma memória principal, onde

o endereço FFF representa a maior posição endereçável.

Todos os números são apresentados em hexadecimal.

Provas

Questão presente nas seguintes provas

832246

Ano: 2011

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: CESGRANRIO

Orgão: Transpetro

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: CESGRANRIO

Orgão: Transpetro

Provas:

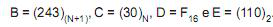

Seja N uma base de numeração, e os números

. Sabendo-se que a igualdade B + D = A + E.C é válida, o produto de valores válidos para a base N é

. Sabendo-se que a igualdade B + D = A + E.C é válida, o produto de valores válidos para a base N é

Provas

Questão presente nas seguintes provas

775335

Ano: 2011

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: CESPE / CEBRASPE

Orgão: SEGER-ES

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: CESPE / CEBRASPE

Orgão: SEGER-ES

Com relação aos sistemas de numeração e representação de dados, à aritmética computacional e às linguagens de programação e arquitetura de computadores, julgue os itens subsequentes.

Em base hexadecimal, a soma dos números 31 e F tem como resultado o número 0100 0110 em base binária.

Provas

Questão presente nas seguintes provas

Cadernos

Caderno Container