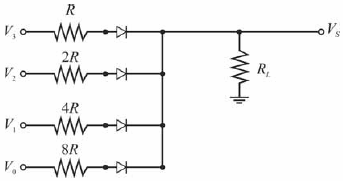

Um conversor D/A de 4 bits com resistores ponderados é projetado conforme o circuito acima. A tensão de entrada assume valor igual a 5 V no nível lógico 1 e zero, caso o sinal lógico esteja no estado zero. A partir dessas informações e considerando R = 10 k!$ Omega !$, RL = 16!$ Omega !$, julgue o item a seguir.

Nesse tipo de conversor D/A implementado, o valor da tensão de saída assume valores sempre menores que a tensão associada a um nível lógico de entrada igual a 1, porque é necessário no projeto que o resistor de carga RL tenha resistência muito inferior à resistência R.

Nesse tipo de conversor D/A implementado, o valor da tensão de saída assume valores sempre menores que a tensão associada a um nível lógico de entrada igual a 1, porque é necessário no projeto que o resistor de carga RL tenha resistência muito inferior à resistência R.

Provas

Questão presente nas seguintes provas