Foram encontradas 40 questões.

Uma área bastante explorada pelos projetistas em sistemas digitais é a de lógica programável, no qual são utilizados dispositivos lógicos programáveis (PLDs). Analise as afirmações sobre os PLDs baseados na tecnologia Field Programmable Gate Array (FPGA), colocando (V) para as verdadeiras e (F) para as falsas.

( ) Sua estrutura interna é baseada em arranjos com ligações fixas de portas E, e ligações variáveis de portas OU.

( ) Para seu armazenamento, faz-se necessária a utilização de uma memória semicondutora externa, por possuir apenas memórias SRAM em seu encapsulamento.

( ) Seus blocos lógicos são interligados por barramentos fixos, fazendo com que a velocidade de processamento entre eles seja previsível.

( ) Suas linguagens de descrição de hardware são várias, dentre elas podemos destacar o VHDL e Verilog.

( ) Essa tecnologia permite executar as mesmas tarefas que são realizadas por circuitos digitais e analógicos.

Assinale a alternativa que contém a sequência CORRETA de cima para baixo.

Provas

Um sistema computacional com endereçamento de dados de 32 bits, utiliza um sistema de cache nível 1 com capacidade de 1 MB, organizada em blocos de 256 bytes e de forma associativa em 4 vias. Qual será o valor de rótulo, índice de conjunto e deslocamento respectivamente que serão utilizados no acesso à memória CACHE quando o endereço 0x01F71B18 for acessado? Assinale a alternativa que responde CORRETAMENTE à questão acima.

Provas

Testes de escalonabilidade são importantes no processo de escalonamento de tarefas de tempo real, pois podem determinar se um conjunto de tarefas é escalonável. Esses testes variam conforme os modelos de tarefas e as políticas definidas em um problema de escalonamento. Associe a coluna da direita com a da esquerda de acordo com as características desses testes.

(1) Testes Exatos

(2) Testes Suficientes

(3) Testes Necessários

( ) É um teste mais restritivo em que conjuntos de tarefas aceitos certamente são escalonáveis.

( ) A única garantia que esse tipo de teste pode fornecer é que os conjuntos descartados de tarefas certamente não são escalonáveis.

( ) São precisos uma vez que indicam se um conjunto de tarefas é ou não escalonável.

Assinale a alternativa que contém a sequência CORRETA de associação, de cima para baixo.

Provas

Sistemas de tempo real (STR) são aqueles em que o comportamento correto do sistema não depende apenas dos valores calculados, mas, também, dos tempos em que os resultados são produzidos. Sobre os sistemas de tempo real, assinale a alternativa INCORRETA.

Provas

- Fundamentos de Sistemas OperacionaisGerenciamento de Recursos de Hardware

- Gerenciamento de ProcessosDeadlock

- Gerenciamento de ProcessosSincronização de Processos

Sistemas computacionais possuem uma série de recursos que são compartilhados através de um sistema operacional entre diversos processos. Muitas vezes, tais recursos necessitam ser acessados de forma exclusiva pelos processos do sistema e, por isso, situações de impasse (deadlock) podem ocorrer. Sobre a ocorrência de impasses, assinale a alternativa INCORRETA.

Provas

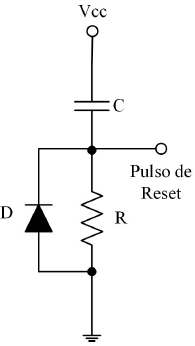

Durante a energização do sistema (power on), o circuito de inicialização (reset) é essencial para garantir que um processador não opere em um nível de tensão em que o dispositivo não tem operação garantida. O sinal de reset para o microcontrolador pode ser aplicado no power on através de um circuito passivo externo ou através de um circuito integrado dedicado. A figura a seguir mostra um circuito passivo de reset baseado em uma rede RC (resistor/capacitor).

Analise as afirmativas a seguir.

I. O sinal de reset do circuito da figura é ativo baixo.

II. Alguns microprocessadores/microcontroladores contêm circuito interno de reset e, dependendo da fonte de alimentação VCC utilizada, podem não requerer um circuito externo para esse fim.

III. O diodo D ajuda a descarregar rapidamente o capacitor quando a tensão de alimentação VCC é desligada.

Assinale a alternativa CORRETA.

Provas

O sistema de memória do computador hipotético “IFSC 2015” possui registrador de endereço de memória com largura de 24 bits e palavra de memória com largura de 32 bits. Considerando 1 Mbyte = 1.048.576 bytes, qual é a capacidade de armazenamento desse sistema de memória, em bytes?

Assinale a alternativa que responde CORRETAMENTE à questão acima.

Provas

O código BCD 8421, que possui como iniciais do nome o significado de Binary Coded Decimal, é uma codificação de 4 bits bastante utilizada na conversão do sistema de numeração decimal para o binário. Existem também, além do BCD 8421, outros códigos que utilizam 4 bits, comopor exemplo o BCD 7421, o BCD 5211, o Excesso 3, o Código Gray, entre outros mais. Associe a coluna da direita, que contém os valores de conversões em decimal, com os seus respectivos códigos que são descritos na coluna da esquerda.

(1) GRAY

(2) BCD 8421

(3) BCD 7421

(4) Excesso 3

(5) BCD 5211

( ) Seu valor referente à numeração decimal 9 é o 1001 em binário.

( ) Seu valor referente à numeração decimal 7 é o 0100 em binário.

( ) Seu valor referente à numeração decimal 4 é o 0111 em binário.

( ) Seu valor referente à numeração decimal 8 é o 1001 em binário.

( ) Seu valor referente à numeração decimal 3 é o 0101 em binário.

Assinale a alternativa que contém a ordem CORRETA de associação, de cima para baixo.

Provas

Qual o comportamento do circuito descrito pelo código abaixo, escrito em Very High Speed Integrated Circuit Hardware Description Language (VHDL)?

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY circuito IS

GENERIC (size: INTEGER := 3);

PORT (Clock, Clear, Load: IN std_logic;

X: IN std_logic_vector(size DOWNTO 0);

Y: OUT std_logic_vector(size DOWNTO 0));

END;

ARCHITECTURE Behavior OF circuito IS

BEGIN

PROCESS (Clock, Clear)

BEGIN

IF Clear = '1' THEN

Y <= (OTHERS => '0');

ELSIF Clock'EVENT AND Clock = '1' THEN

IF Load = '1' THEN

Y <= X;

END IF;

END IF;

END PROCESS;

END;

Assinale a alternativa que responde CORRETAMENTE à questão acima.

Provas

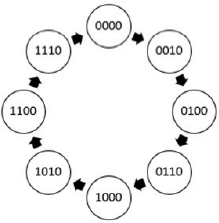

Os circuitos digitais sequenciais são projetados levando em consideração as informações atuais das entradas, geradas através de portas lógicas combinacionais e, também, das informações dos estados anteriores, sendo este através de elementos de memória. Qual o circuito sequencial representado pelo diagrama da figura abaixo?

Assinale a alternativa que responde CORRETAMENTE à questão acima.

Provas

Caderno Container