Foram encontradas 40 questões.

Um sistema com microcontrolador da família PIC possui a seguinte programação:

void interrupt();

void main()

{

RCON.IPEN = 1;

INTCON.GIE = 1;

INTCON.PEIE = 1;

INTCON.INT0IE = 1;

INTCON2.RBPU = 1;

INTCON2.INTEDG0 = 1;

ADCON1 = 0b00001111;

TRISB.RB0 = 1;

TRISD = 0b00000000;

PORTD = 0b10101010;

while(1);

}

void interrupt() {

if(PORTB.RB0 == 0) {

PORTD=~PORTD;

while(portb.rb0 == 0);

}

}

Como pode ser explicado o comportamento dos pinos de I/O deste sistema microcontrolado?

Provas

Uma das aplicações do transistor é em amplificadores de potência.

A respeito do modo de polarização de um amplificador a transistor, como deve ser polarizado o transistor de um amplificador classe AB e como fica a amplificação do sinal?

Provas

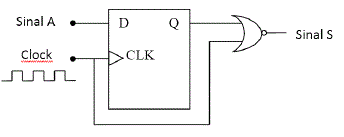

Considere o sinal “A” ligado na entrada do Flip-Flop tipo D, com o sinal de clock ligado na porta NOR conforme circuito abaixo.

Sabendo que a entrada “A” é um sinal assíncrono, isto é, pode mudar de estado a qualquer momento em relação ao sinal do clock.

Escolha a alternativa correta que representa a forma de onda que apresenta o sinal de saída “S”.

Provas

Uma porta E simples, em linguagem VHDL, pode ser assim descrita:

library IEEE;

use IEEE.std_logic_1164.all;

entity ANDGATE is

port (

I1 : in std_logic;

I2 : in std_logic;

O : out std_logic);

end entity ANDGATE;

architecture RTL of ANDGATE is

begin

O <= I1 and I2;

end architecture RTL;

Fonte: Astral Científica. CPLD Trainer. Curitiba: 2013.

Com relação aos blocos que compõem a estrutura de um programa em VHDL, é correto afirmar que:

Provas

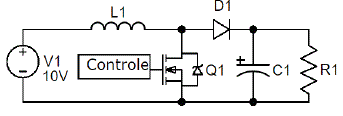

O circuito abaixo representa um tipo de conversor de tensão. Sabe-se que a tensão em R1 é 12V.

Como é chamado este conversor e qual a sua razão de trabalho?

Provas

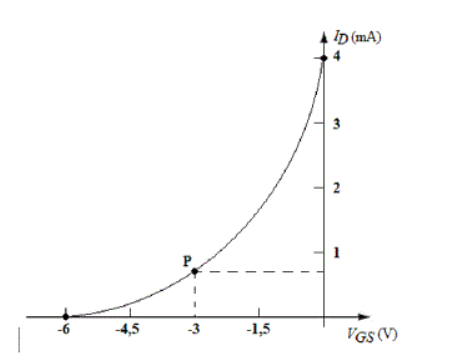

O modelo equivalente CA de um FET necessita do conhecimento e/ou cáculos de determinados parâmetros, como da admitância gm e das resistências de entrada – entre a porta e a fonte – e de saída – entre o dreno e a fonte. Para tal, pode ser analisada sua característica VGS x ID, conforme o exemplo a seguir:

Para o FET de parâmetros descritos pelo gráfico considerar também que:

-Máximo valor de gm dado pela relação

gm0 = !$ \dfrac{2.I\ DSS}{\left|VP\right|} !$ ;

-Admitância yos = 0,25 μS;

-Resistência infinita de entrada.

Qual será o modelo equivalente CA do FET descrito?

Provas

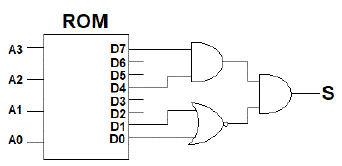

Na figura, está esquematizado um circuito lógico, acionado através da utilização dos pinos de endereço e leitura de dados de uma memória ROM.

Considere que:

- Tanto os pinos de endereçamento quanto de dados operam em modo ativo alto.

- O módulo de tensão dos pinos de dados, em nível alto, é suficiente para ativar as entradas das portas lógicas.

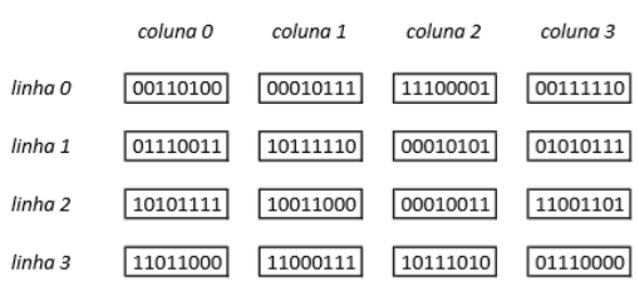

Adicionalmente, é apresentado o esquemático da matriz quadrada de registradores desta ROM, com as respectivas palavras de oito bits gravadas em cada registrador:

Assinale a alternativa que apresenta os níveis lógicos dos pinos de endereçamento que, conforme o circuito proposto pela figura, proporcionarão S = 1.

Provas

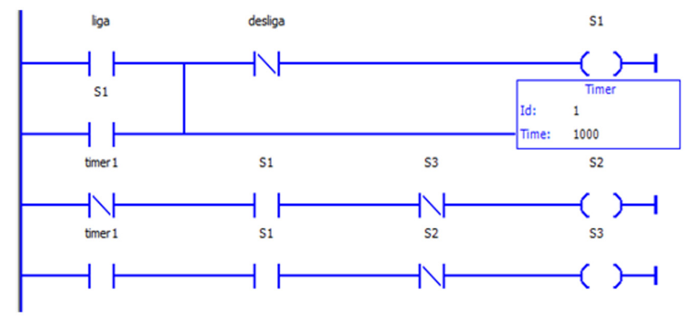

Os controladores lógicos programáveis, podem ser programados por quatro métodos. Ladder, Blocos de Função, listagem de instruções e código estruturado.

Verifique qual a função que o CLP programado com o diagrama ladder apresentado irá executar, quando a entrada liga for acionada.

Provas

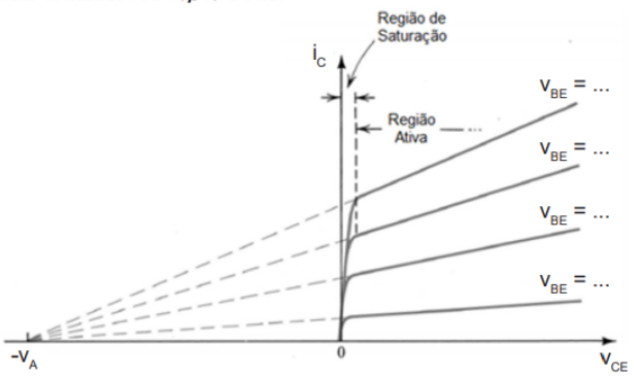

A figura apresenta a característica iC x VCE de um transistor npn real.

Fonte: SEDRA, A. S.; SMITH, K. C. Microeletrônica. 5. ed. São Paulo: Pearson, 2007

Notam-se os valores não constantes de iC , conforme o aumento de VCE. Também está presente a Tensão de Early (VA), outro parâmetro importante no que se refere à relação entre a corrente e a tensão citadas.

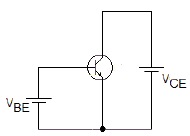

Considere determinado transistor npn real, com VA = 50V, em configuração emissor comum, conforme figura.

Inicialmente, tem-se VCE = 6V, além de VBE apresentar um valor tal que a corrente de emissor atinja 2,24mA.

Num segundo momento, VBE é mantida constante, com VCE diminuindo para 2V. Qual será o novo valor da corrente de coletor?

Provas

Para testar o valor de uma variável em um sistema utilizando um microcontrolador da Linha PIC 16F, o programador utilizou as seguintes linhas de código:

MOVF VARIAVEL,W

XORLW .127

BTFSS STATUS,Z

Durante a execução do programa no microcontrolador, em determinada passagem pelas linhas de código aqui descritas, se o valor da variável VARIAVEL for 0xFF, qual será o valor armazenado no registrador W, após a execução da linha “XORLW .127”?

Provas

Caderno Container