Foram encontradas 45 questões.

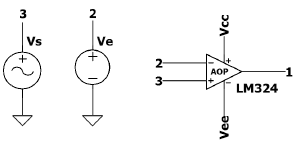

Usando o CI LM324, deseja-se gerar um sinal retangular com frequência de 5 kHz com tensão mínima de -5 V, tensão máxima de 5 V e largura de pulso de 25 % do período do sinal gerado. Para isso, dispomos de uma fonte senoidal Vs de 10 mV de amplitude e frequência de 5 kHz e uma fonte DC ajustável Ve, a tensão de alimentação Vcc = 5 V, Vee = -5 V. Considerando a tensão de offset do amplificador operacional nula, qual deve ser o valor da fonte Ve para que o objetivo seja atingido?

Provas

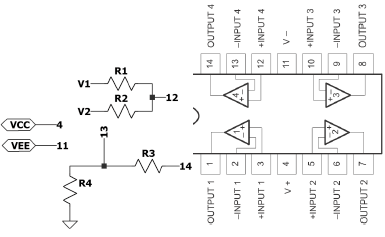

O circuito cujo esquema de conexões é apresentado na figura a seguir foi construído com o LM324, cujo esquema de configurações de pinos é também apresentado. Neste circuito, R1 = 2 kΩ, R2 = 3 kΩ, R3 = 9 kΩ, R4 = 1 kΩ, VCC = 10 V, VEE = - 10 V. Considerando que os valores máximos e mínimos de V1 e V2 sejam ± 10 mV, que tipo de saída é produzido pelo circuito em questão?

Provas

No circuito conversor AD paralelo de três bits da figura a seguir, os comparadores são ideais. Quando Vs = 0 V, a saída do decodificador será D0 = 0, D1 = 0 e D2 = 0, e quando Vs = VREF, a saída do decodificador será D0 = 1, D1 = 1 e D2 = 1. Qual deve ser o nível de tensão da fonte Vs para que a saída do decodificado seja D0 = 1, D1 = 0 e D2 = 1?

Provas

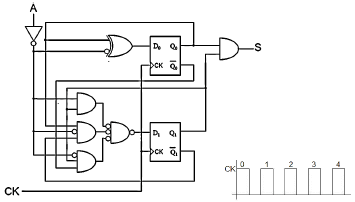

Considere o estado inicial (pulso 0) do circuito seqüencial, apresentado na figura a seguir como: (A = 1; Q0 = 1; Q1 = 0; S0 = 0). Se o circuito receberá 4 pulsos de clock consecutivos (1, 2, 3 e 4), quais os estados assumidos pela saída S após cada pulso de clock?

Provas

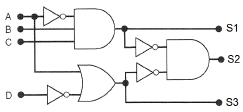

Avalie o circuito lógico da figura a seguir e determine os estados das saídas S1, S2 e S3, quando os sinais de entrada estiverem nos seguintes níveis lógicos: (A = 1, B = 0, C = 0, e D =1).

Provas

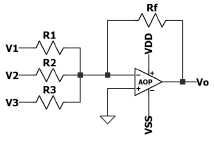

No circuito a seguir, o dispositivo AOP é um amplificador operacional ideal com ganho de malha aberta infinito. O circuito está dimensionado para que Vo esteja sempre dentro dos limites entre VDD e VSS, onde VSS = -VDD. Sendo Rf = 20 kΩ, R1 = 1 kΩ, R3 = 5 kΩ, V1 = 2xV2, e V3 = 3xV1, calcule R2 para que o circuito produza a saída Vo = -37xV1.

Provas

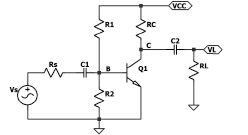

No circuito amplificador a seguir, o sinal a ser amplificado é fornecido pela fonte Vs, que é AC senoidal com 10 mV de pico e frequência de 10 kHz. Para a seguinte análise, a resistência de fonte Vs pode ser considerada nula. O nó VCC está conectado a uma fonte DC ideal de 10 V, neste circuito R1 = 100 kΩ, R2 = 6,65 kΩ, RC = 20 kΩ, RL = 20 kΩ, e para a frequência de interesse, as impedâncias das capacitâncias C1 e C2 podem ser consideradas nulas. O nível DC de polarização do nó C é igual VCC/2, a corrente de base do transistor Q1 pode ser considerada desprezível e a tensão early VA do mesmo pode ser considerada infinita. A parcela AC da corrente de coletor é dada por Ic-AC = (Ic-DC/VT)xVbe-AC, onde VT é a tensão térmica da junção pn que na temperatura ambiente pode ser considerada aproximadamente 25 mV.Calcule o ganho de tensão deste circuito entre VL e Vs.

Provas

O circuito a seguir é um dimmer ajustado para que a carga RL de 12,5 Ω seja conectado à fonte V1, AC senoidal com tensão de pico Vp = 127 V e frequência de 60 Hz, apenas durante o quarto final de cada semiciclo do sinal da fonte Vin. Supondo que quando o TRIAC opera como chave fechada a resistência do mesmo seja desprezível quando comparada com a resistência da carga RL, qual o valor da corrente máxima atravessando a carga RL?

Provas

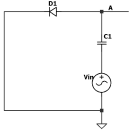

No circuito a seguir, o diodo é ideal, ou seja, a tensão VD de polarização direta é nula e a tensão de ruptura reversa é infinita, o capacitor C1 = 1 μF, a fonte Vin é AC senoidal com tensão de pico Vp = 110 V e frequência de 60 Hz. Considerando que o circuito já está operando em regime permanente, quais os valores da tensão máxima e tensão média no nó A, respectivamente?

Provas

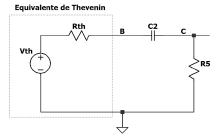

No circuito a seguir, quais os valores da tensão e da resistência de Thevenin, Vth e Rth, que farão com que este circuito produza no nó C o mesmo resultado do circuito da questão anterior, para sinais com frequências iguais ou maiores do que 1 kHz? Considere os mesmos valores das resistências e capacitâncias do circuito da figura descrita na questão anterior.

Provas

Caderno Container