Foram encontradas 50 questões.

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: UFRN

Orgão: UFERSA

Uma memória cache associativa por conjunto – contendo 2 conjuntos e 256 linhas, cada linha possuindo 16 bytes – tem capacidade de armazenamento de

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: UFRN

Orgão: UFERSA

Uma memória cache segue uma política de substituição de linhas em que um dado, ao ser comandado pelo processador para escrita na hierarquia de memórias, ocorrendo um acerto (hit), é gravado tanto na cache como na memória principal. Essa política é a

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: UFRN

Orgão: UFERSA

Numa hierarquia de memórias, usa-se costumeiramente uma memória cache que tem uma ‘velocidade’ maior que a memória principal. O custo de armazenamento por byte, porém, é mais alto. Em comparação com uma memória principal, a capacidade de armazenamento de uma memória cache é

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: UFRN

Orgão: UFERSA

O arranjo da via de dados que explora o paralelismo de instruções em um fluxo sequencial, que é completamente invisível ao programador, mas melhora o desempenho final da execução de um código é o

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: UFRN

Orgão: UFERSA

Numa via de dados, o bloco lógico que controla a geração de sinais os quais identificam as operações a serem realizadas na Unidade Lógica e Aritmética e os registradores envolvidos nessas operações, denomina-se

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: UFRN

Orgão: UFERSA

Observe o mapa de Karnought a seguir.

|

|

00 | 01 | 11 | 10 |

| 00 | ||||

| 01 | 1 | 1 | 1 | 1 |

| 11 | ||||

| 10 | 1 | 1 | 1 | 1 |

Uma expressão que gera esse mapa é

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: UFRN

Orgão: UFERSA

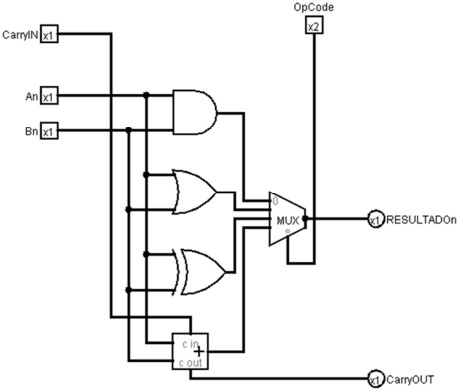

Observe o circuito de uma unidade lógica e aritmética elementar a seguir.

Quando o OpCode desse circuito estiver nos níveis lógicos 102, a operação de saída dessa ULA será

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: UFRN

Orgão: UFERSA

Analise o circuito combinacional a seguir.

Esse circuito contém um codificador e um decodificador de hamming que permite a detecção e correção de erros de transmissão de dados. Considerando os valores lógicos d0=0, d1=1, d2=0 e d3=1, e que a transmissão sofreu uma mudança de valor lógico na linha d1-D1, passando para 0 o valor lógico de saída da transmissão nessa linha, os valores dos sinalizadores s0, s1, s2 e s3 são, respectivamente

Provas

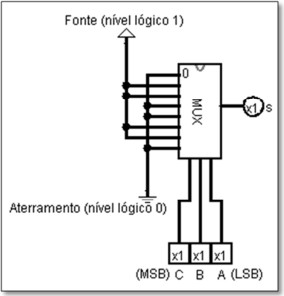

Observe o circuito abaixo.

Esse circuito implementa a seguinte expressão lógica

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: UFRN

Orgão: UFERSA

Flip-flops e latches são comuns em projetos de circuitos digitais sequenciais. Os Flip-flops mais comuns são do tipo D, T e JK. O projeto de circuitos pode seguir abordagens distintas. Uma delas usa as entradas CLEAR e PRESET dos flip-flops. O efeito dessas entradas assíncronas nos flip-flops é:

Provas

Caderno Container