Foram encontradas 20 questões.

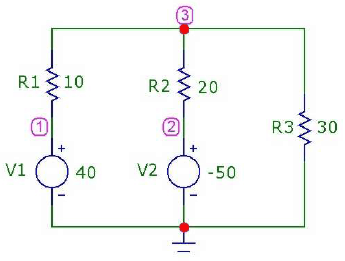

Observe a figura abaixo.

No circuito acima, V1=40V, V2=-50V, R1=10Ω, R2=20Ω e R3=30Ω. Respectivamente, a potência dissipada pela fonte de tensão V1 do nó “1” em relação ao nó terra e a potência dissipada pela fonte de tensão V2 do nó “2” em relação ao nó terra são, aproximadamente,

Provas

Questão presente nas seguintes provas

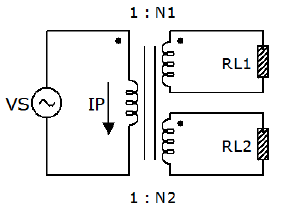

Observe a figura abaixo.

No circuito da figura acima, o transformador ideal de duas derivações é alimentado no primário com uma fonte de tensão VS senoidal de frequência igual a 60 Hertz, de valor RMS igual a 2 Volts e valor médio igual a zero Volts. Cada uma das derivações alimenta uma resistência de valor 8 Ohms (RL1 e RL2). Sendo as relações de transformação para as duas derivações, N1 e N2, respectivamente iguais a 2 e 4, a potência média fornecida pela fonte VS e a corrente RMS do primário, nesta ordem, valem, aproximadamente,

Provas

Questão presente nas seguintes provas

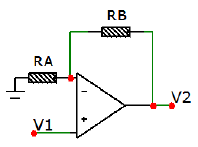

Observe a figura abaixo.

No circuito da figura acima, sendo a tensão no ponto V1 igual a 8 Volts, o resistor RA igual a 10000 Ohms, o resistor RB igual a 15000 Ohms e o amplificador operacional ideal, a tensão no ponto V2 vale, aproximadamente,

Provas

Questão presente nas seguintes provas

Observe a tabela abaixo.

| Dispositivo | Quantidade de endereços | |

| (SEM USO) | FIM: FFFF | |

| SAÍDA | 2KB | |

| ENTRADA | 2KB | |

| RAM | 16KB | |

| ROM | 8KB | INÍCIO: 0 |

Um sistema baseado em Microprocessador tem o mapeamento de memória descrito na tabela acima. A partir do endereço zero, é colocada uma ROM de 8KB, logo a seguir uma RAM de 16KB, e assim sucessivamente, conforme a tabela. Para esta configuração, os endereços, em hexadecimal, iniciais e finais da RAM e da SAÍDA, são, respectivamente,

Provas

Questão presente nas seguintes provas

Dada a função lógica F = A·/B·/C·D + A·/B·C·/D + A·/B·C·D + A·B·/C·D + A·B·C·/D + A·B·C·D (Notação: “/” significa “NÃO”, “·” significa “E”, e “+” significa “OU”.).

A expressão simplificada dessa função lógica é

Provas

Questão presente nas seguintes provas

No código, a instrução “MOV V, #W” significa “V recebe o valor W”, e “ADD X, Y, Z” significa “X recebe Y somado com Z”.

MOV A, #2

MOV B, #3

MOV C, #2

ROTINA:

ADD A, A, B

ADD B, A, -1

ADD C, C, -1

SE C≠0 SALTA PARA ROTINA

FIM:

SALTA PARA FIM

Para o programa Assembly de microprocessador dado acima, no qual cada instrução é executada em 1 (um) ciclo de relógio, qual o resultado final nos registradores “A”, “B” e “C” após 30 ciclos de relógio?

Provas

Questão presente nas seguintes provas

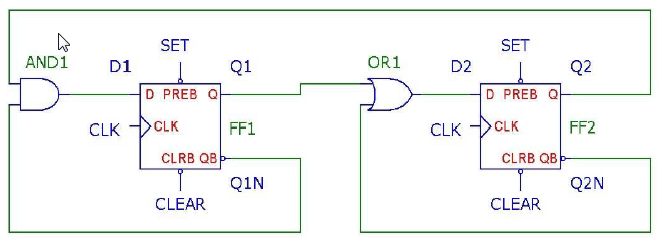

Observe a figura abaixo.

No circuito acima, com componentes ideais, considere que as saídas Q1 e Q2 dos Flip-Flops FF1 e FF2 estão em valor lógico zero (0 lógico) antes de ser aplicado o sinal de relógio “CLK”. Após o início da aplicação do relógio, os sinais SET e CLEAR permanecem com valor lógico um (1 lógico). As saídas Q1, Q2, D1 e D2 assumem, respectivamente, os seguintes valores a cada pulso de relógio:

Provas

Questão presente nas seguintes provas

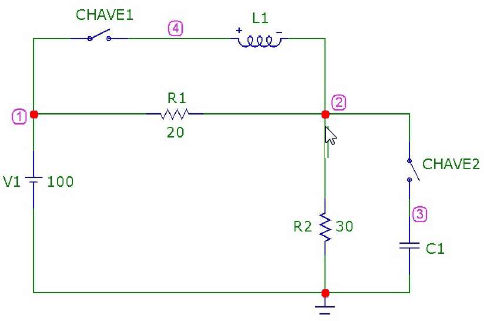

Observe a figura abaixo.

No circuito acima, V1=100V, R1=20Ω, R2=30Ω, indutor L1 e capacitor C1 têm valor indeterminado. Antes das chaves CHAVE1 e CHAVE2 serem fechadas, L1 e C1 estão sem energia armazenada. Respectivamente, em relação ao nó terra, o valor da tensão no nó “2” antes das chaves fecharem simultaneamente; o valor da tensão no nó “2” imediatamente após as chaves fecharem simultaneamente; e o valor da tensão no nó “2” após as chaves estarem ambas fechadas por 100 minutos são, aproximadamente,

Provas

Questão presente nas seguintes provas

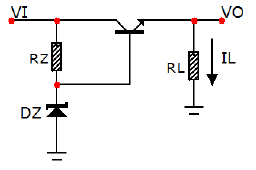

Observe a figura abaixo.

Na figura acima, considerando que o diodo zener DZ ideal tem valor nominal de 5,6 Volts, que o beta (ganho de corrente DC) do transistor bipolar vale 420, que a tensão base-emissor vale 0,7 Volts, que a tensão VI vale 9 Volts, que os resistores RZ e RL valem ambos 100 Ohms, a corrente IL vale, aproximadamente,

Provas

Questão presente nas seguintes provas

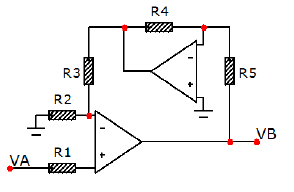

Observe a figura abaixo.

No circuito da figura acima, sendo os amplificadores operacionais ideais, a tensão no ponto VA igual a 1 Volt, os resistores R1, R2, R3, R4 e R5, respectivamente, iguais a 1000 Ohms, 1000 Ohms, 10000 Ohms, 4000 Ohms e 1000 Ohms, a tensão no ponto VB vale, aproximadamente,

Provas

Questão presente nas seguintes provas

Cadernos

Caderno Container