Foram encontradas 800 questões.

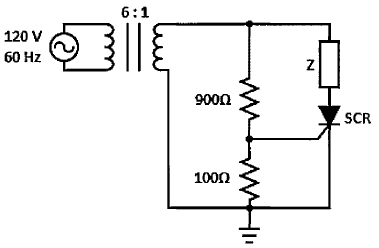

Analise o circuito abaixo para uma carga genérica Z considerando que o SCR possui tensão de disparo do gatilho e corrente de disparo do gatilho, respectivamente, VGT = 0,982 V e IGT = 200 μA, e sua corrente de manutenção é desprezível:

Assinale a opção que apresenta o ciclo de trabalho (Duty Cycle) do SCR.

Provas

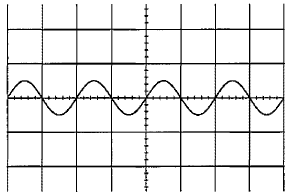

Observe a figura abaixo:

A figura acima mostra a tela de um osciloscópio que foi configurado na escala vertical com 10V/div e na escala horizontal com 2ms/div. Com base nos dados, determine a frequência, o valor eficaz e o valor médio do sinal medido respectivamente, e assinale a opção correta.

Provas

Com relação às características e benefícios de um sistema com CLP (Controladores Lógicos Programáveis), assinale a opção INCORRETA.

Provas

Coloque (F) falso ou (V) verdadeiro nas afirmativas abaixo, em relação aos conversores digital-analógico e analógico-digital, assinalando a seguir a opção correta.

( ) A resolução percentual de um DAC depende unicamente do número de bits.

( ) O erro de fundo de escala soma um pequeno valor positivo ou negativo à saí da analógica esperada para qualquer entrada digital.

( ) O erro de offset é o desvio máximo do valor ideal de saída do DAC, expresso como porcentagem do fundo de escala.

( ) Um DAC é monotônico se sua saída aumenta conforme a entrada binária é incrementada de um valor para o seguinte.

( ) A tensão de saída VAX de um ADC de rampa digital é uma forma de onda do tipo escada que aumenta em passos discretos até exceder a tensão de entrada, VA. O fato de que VAX não aumenta de maneira contínua, mas em degraus, provoca uma diferença entre a quantidade real (analógica) e o valor digital associado. Isso é denominado erro de quantização.

Provas

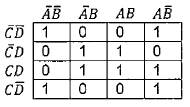

A partir do mapa de Karnaugh (mapa K) abaixo, determine a expressão mínima de saída e assinale a opção correta.

Provas

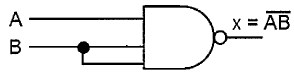

Observe a figura abaixo:

Com relação às famílias lógicas de circuitos integrados (Cls) TTL e MOS, analise as afirmativas a seguir:

I- Os Cls MOS podem acomodar um número muito maior de elementos de circuito em um único chip do que Cls bipolares.

II- Em qualquer CI TTL, todas as entradas serão 1s se não estiverem conectadas a algum sinal lógico ou a GND.

III- A principal desvantagem dos dispositivos TTL é o risco de serem danificados por eletricidade estática. Embora isso possa ser minimizado por procedimentos adequados de manuseio, os MOS são muito mais duráveis.

IV- Sempre que duas (ou mais) entradas TTL na mesma porta são conectadas para formar uma entrada comum, como apresentado na figura acima, essa entrada comum representará uma carga que é a soma das correntes de carga de entrada individual.

Assinale a opção correta.

Provas

Com relação ao diodo semicondutor, assinale a opção INCORRETA.

Provas

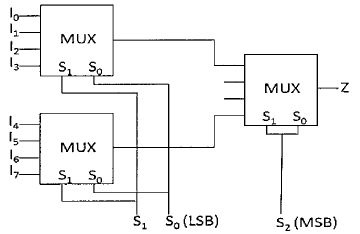

Observe o circuito abaixo:

Determine a função desempenhada pelo circuito acima e assinale a opção correta.

Provas

Sabendo que o custo da energia elétrica é de 7 centavos por kilowatt-hora. Calcule o custo semanal de uma lavanderia que dispõe de 5 máquinas de lavar de 500 W usadas durante 10 horas por dia em 7 dias na semana e assinale a opção correta.

Provas

Um DAC de quatro bits usa resistores com ponderação binária. Se o resistor LSB for de 16 !$ k Ω !$, qual será o valor do MSB?

Provas

Caderno Container