Foram encontradas 315 questões.

Uma Unidade Central de Processamento possui um contador de programas 64 bits e o barramento de dados deste processador também é de 64 bits. Para realizar uma operação de soma de dois operandos em uma única etapa, o registrador de instruções informa à unidade lógica aritmética a instrução a ser realizada e os dados a serem processados. Sabendo que a instrução é armazenada em uma palavra de 12 bits e o resultado da operação não pode exceder 64 bits, qual o tamanho máximo em bits do registrador de instruções e o tamanho máximo em bits de cada operando?

Provas

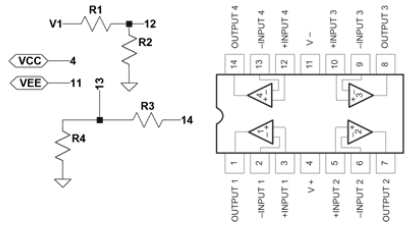

Considerando ainda o circuito apresentado na questão anterior, com as mesmas configurações apresentadas, exceto pela fonte V1, qual o valor máximo da tensão de pico da fonte V1 para que a saída do amplificador continue operando na região linear, ou seja, sem ocorrer saturação do sinal?

Provas

Usando o amplificador operacional LM324, construímos o circuito cujo esquema de conexões e configurações de pinos é apresentado na figura a seguir:

Considerando que os valores máximo e mínimo de V1 sejam ±10 mV, qual a saída produzida pelo circuito?

Provas

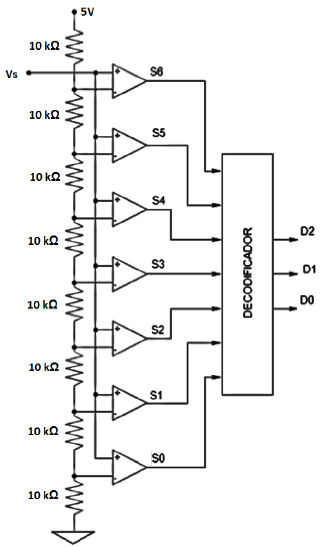

Um conversor AD paralelo de três bits é apresentado na figura a seguir, onde seus comparadores são ideias. As saídas estão calibradas para (D1, D2, D3) = (0, 0, 0), quando Vs<0,625 V e (D1, D2, D3) = (1, 1, 1) e quando Vs>4,375 V:

Qual será o estado da saída do conversor quando a entrada Vs estiver no intervalo 3,21 V<Vs<3,43 V?

Provas

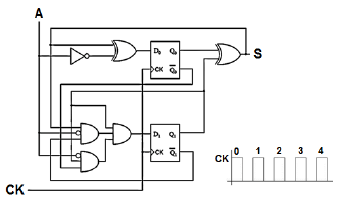

No circuito sequencial apresentado na figura a seguir, o estado inicial (pulso 0) apresenta os seguintes estados A=0, Q0=1, Q1=1 e S0=1:

Após o circuito receber quatro pulsos de clock consecutivos (1, 2, 3 e 4), quais os estados assumidos pela saída S após cada pulso de clock?

Provas

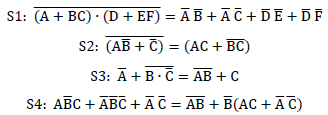

Avalie as seguintes expressões lógicas:

Assinale a alternativa CORRETA:

Provas

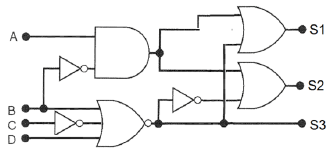

Avalie o circuito lógico a seguir:

Os estados das saídas S1, S2 e S3, quando os sinais de entrada estiverem nos níveis lógicos: A=1, B=1, C=0 e D=0, são:

Provas

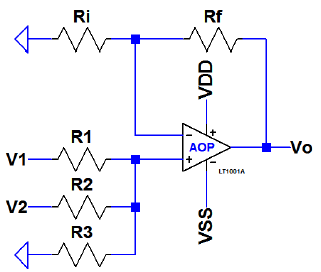

O circuito com amplificador operacional (AOP) abaixo está dimensionado para que Vo esteja sempre dentro dos limites entre VDD e VSS, onde VSS=−VDD. O AOP pode ser considerado ideal com ganho de malha aberta infinito:

Sabendo que R1=R2=R3=60 kΩ, podemos afirmar que Vo em função de V1 e V2 fica:

Provas

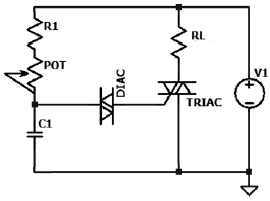

O circuito a seguir é um dimmer ajustado para que a carga RL seja conectada à fonte V1, AC senoidal com tensão de pico Vp=110 V e frequência de 50 Hz, apenas durante o sexto final de cada semiciclo do sinal da fonte Vin:

Supondo que o TRIAC opera como chave fechada e que a resistência do mesmo seja desprezível quando comparada com a resistência da carga RL e sabendo que a corrente máxima que atravessa a carga é de 10 A, podemos afirmar que o valor da resistência da carga RL é:

Provas

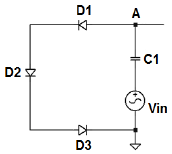

No circuito a seguir, os diodos podem ser considerados ideais, ou seja, a tensão VD de polarização direta é nula e a tensão de ruptura reversa é infinita. Para o capacitor é C1=10 μF. A fonte Vin é AC senoidal com tensão de pico Vp=127 V e frequência de 50 Hz:

Considerando que o circuito esteja operando em regime permanente, os valores da tensão mínima e tensão média no nó A valem, respectivamente:

Provas

Caderno Container