Foram encontradas 20.584 questões.

Com relação às grandezas elétricas, é INCORRETO afirmar:

Provas

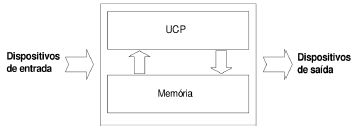

A figura a seguir representa a arquitetura de computador proposta por Von Neumann. Nesta arquitetura, a Unidade Central de Processamento (UCP) é composta por uma unidade lógica aritmética, unidade de controle, contador de programa e registradores. Durante a execução de um programa nesta arquitetura, o componente que armazena a posição da memória onde encontra-se a próxima instrução a ser executada pela UCP chama-se:

Provas

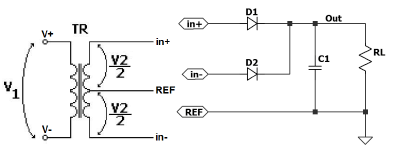

No circuito da figura a seguir, as entradas in+ e insão conectadas ao secundário de um transformador TR, cujo primário é conectado à rede elétrica de 60 Hz e 127 V e fornece uma saída entre in+ e in- de 25,4 V. Este transformador possui uma derivação central REF. Os diodos do circuito são todos de silício com VD = 0,7 V e tensão de ruptura avalancha maior que 100 V, a carga RL é de 1 kΩ e o capacitor C1 é de 100 μF. Qual o valor aproximado da tensão de ripple deste circuito retificador?

Provas

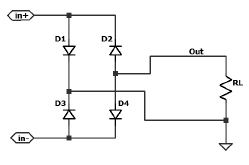

As entradas in+ e in- do circuito da figura a seguir são conectadas ao secundário de um transformador, cujo primário é conectado à rede elétrica de 60 Hz e 127 V e fornece uma saída no secundário de 12,7 V. Os diodos do circuito são todos de silício com VD = 0,7 V e tensão de ruptura avalancha maior que 100 V, e a carga RL é de 1 kΩ. Qual a frequência do sinal e tensão de pico no nó Out?

Provas

Um computador adquirido com 4k de memória, ou 212 palavras de memória, possui um processador cujo registrador de endereços de memória é de 16 bits e o barramento de dados é de 20 bits. Qual a capacidade máxima de memória adicional endereçável por este processador e qual o tamanho do dado, em bits, armazenado em cada posição da memória?

Provas

Considere um processador com uma Unidade Central de Processamento cujo contador de programas é de 32 bits e o registrador de instruções é de 74 bits. Além do código de operação, cada instrução possui dois operandos de 32 bits. Quais são, respectivamente, o tamanho da instrução e o tamanho do código de operação deste processador?

Provas

No circuito conversor AD paralelo de três bits da figura a seguir, os comparadores são ideais. Quando Vs = 0 V, a saída do decodificador será D0 = 0, D1 = 0 e D2 = 0, e quando Vs = VREF, a saída do decodificador será D0 = 1, D1 = 1 e D2 = 1. Qual deve ser o nível de tensão da fonte Vs para que a saída do decodificado seja D0 = 1, D1 = 0 e D2 = 1?

Provas

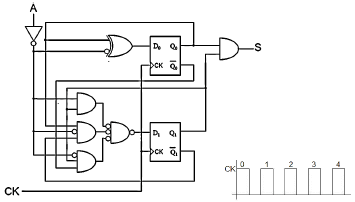

Considere o estado inicial (pulso 0) do circuito seqüencial, apresentado na figura a seguir como: (A = 1; Q0 = 1; Q1 = 0; S0 = 0). Se o circuito receberá 4 pulsos de clock consecutivos (1, 2, 3 e 4), quais os estados assumidos pela saída S após cada pulso de clock?

Provas

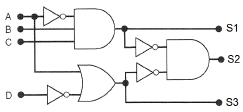

Avalie o circuito lógico da figura a seguir e determine os estados das saídas S1, S2 e S3, quando os sinais de entrada estiverem nos seguintes níveis lógicos: (A = 1, B = 0, C = 0, e D =1).

Provas

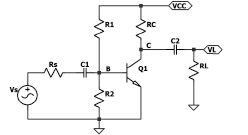

No circuito amplificador a seguir, o sinal a ser amplificado é fornecido pela fonte Vs, que é AC senoidal com 10 mV de pico e frequência de 10 kHz. Para a seguinte análise, a resistência de fonte Vs pode ser considerada nula. O nó VCC está conectado a uma fonte DC ideal de 10 V, neste circuito R1 = 100 kΩ, R2 = 6,65 kΩ, RC = 20 kΩ, RL = 20 kΩ, e para a frequência de interesse, as impedâncias das capacitâncias C1 e C2 podem ser consideradas nulas. O nível DC de polarização do nó C é igual VCC/2, a corrente de base do transistor Q1 pode ser considerada desprezível e a tensão early VA do mesmo pode ser considerada infinita. A parcela AC da corrente de coletor é dada por Ic-AC = (Ic-DC/VT)xVbe-AC, onde VT é a tensão térmica da junção pn que na temperatura ambiente pode ser considerada aproximadamente 25 mV.Calcule o ganho de tensão deste circuito entre VL e Vs.

Provas

Caderno Container