Foram encontradas 20.455 questões.

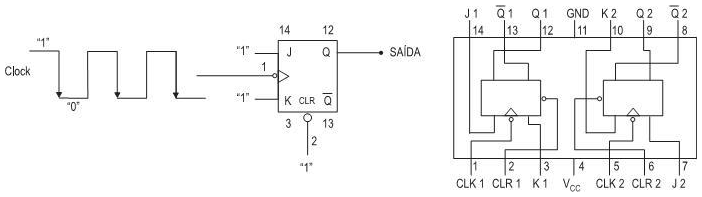

Sabe-se que o CLEAR está em “0”, que o flip-flop apresenta saídas Q = “0” e Q = “1”, que a transição ocorre na descida do clock (conforme pode ser visto na mesma Figura) e que a frequência é compatível com as características do CI. (A fonte de alimentação e o terra foram omitidos, propositadamente, para não sobrecarregar o desenho.)

Se “1”, um lógico, representa nível alto, e “0”, zero lógico, representa nível baixo, qual é a frequência do sinal na saída, tomado em Q, com relação à frequência do clock?

Provas

Provas

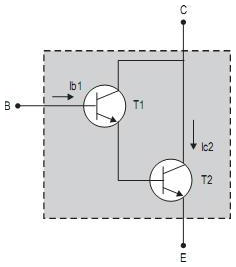

Considerando-se, para fins de cálculo, que, para ganhos de corrente CC (corrente contínua) Ic/Ib > 100 a corrente de coletor Ic é igual à corrente de emissor Ie, e sabendo-se ainda que B1 = 150 e B2 = 200, o ganho total Ic2/ Ib1 da configuração apresentada será

Provas

- Álgebra Booleana e Circuitos Lógicos

- Contadores em Engenharia Eletrônica

- Eletrônica Digital na Engenharia Eletrônica

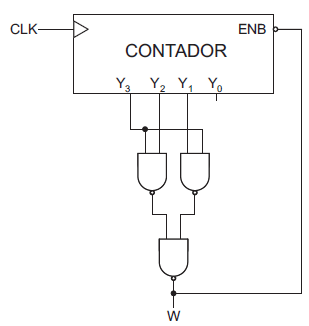

Neste circuito, emprega-se um sinal de clock (CLK) com um período de 10 segundos.

Provas

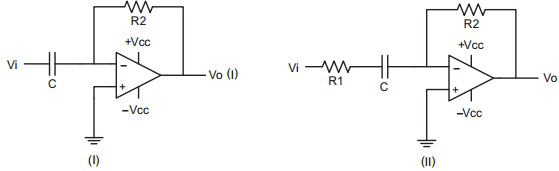

Comparando-se os dois circuitos, constata-se que o(a)

Provas

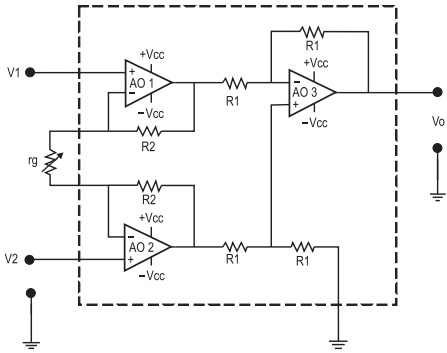

Quando comparado a um circuito am- plificador operacional de uso corrente, algumas características podem ser destacadas, entre as quais a tensão de OFFSET de entrada muito baixa, a alta rejeição de modo comum, o ganho de malha aberta extremamente alto, a impedância de saída muito baixa e a impedância de entrada alta. Em alguns desses CI dedicados à instrumentação, certos parâmetros não estão limitados apenas às suas características intrínsecas, podendo ser ajustados ex- ternamente, como é o caso do ganho de malha fechada, controlado por um resistor de precisão (rg) também mostrado na Figura.

Sabendo-se que R1= 10 k Ω, R2=100 k Ω, e que rg foi ajustado para 1 kΩ, , qual é o valor da tensão de saída Vo, em volts, quando V2=1,001 V e V1=1,000 V ?

Provas

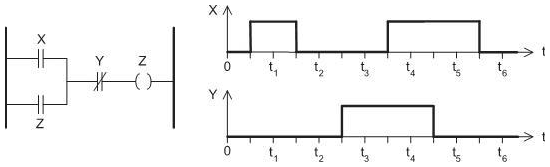

Sabendo-se que em t = 0 o nível lógico de Z = 0, analisando-se os diagramas da Figura nos instantes de tempo assinalados, os instantes em que Z = 1 são:

Provas

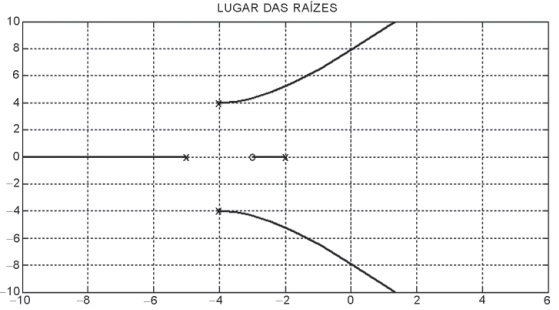

Entre esses sistemas, é instável o que está representado em:

Provas

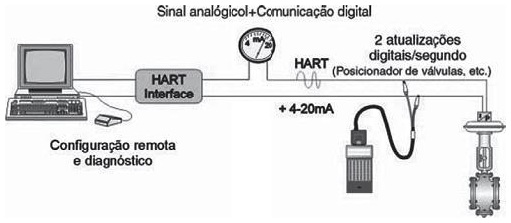

O Protocolo HART possibilita a comunicação digital bidirecional em instrumentos de campo inteligentes, sem interferir no sinal analógico de 4-20 mA. Usando-se o padrão Bell 202, de chaveamento por deslocamentos de frequência (FSK), para sobrepor os sinais de comunicação digital ao de 4-20 mA, e por ser o sinal digital FSK simétrico em relação ao zero, no Protocolo HART, observa-se que a lógica “1” e a lógica “0”, respectivamente, são representadas, em Hz, por frequências de

Provas

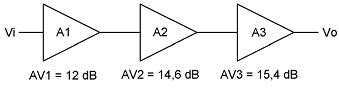

Levando-se em consideração o fato de que os ganhos de tensão de cada estágio — AV1, AV2 e AV3 — estão em decibéis (dB), verifica-se que o ganho total em AV = Vo/Vi também em dB, é de

Provas

Caderno Container