Foram encontradas 447 questões.

Com relação à arquitetura PC padrão, é INCORRETO afirmar que

Provas

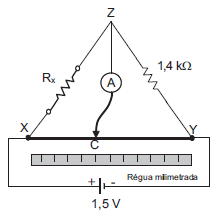

Deseja-se efetuar a medida de uma resistência desconhecida (Rx), improvisando-se o processo mostrado na figura acima. Usa-se uma pilha de 1,5 V alimentando um pedaço de fio resistivo homogêneo de 50 cm esticado ao lado de uma régua milimetrada (segmento XY). Um cursor C mantém contato com o fio resistivo e o amperímetro A indica a presença de corrente entre os pontos Z e C. O método consiste em deslocar o cursor sobre o fio resistivo até zerar a corrente no amperímetro. Feita a experiência, verificouse que a distância YC foi de 35 cm.

O valor de Rx, em \( \Omega \), é:

Provas

Considere a arquitetura implementada a seguir.

entity CONTADOR is

port (CLK, EN, CLR, LOAD, UP: in std_logic;

D: in std_logic_vector (3 downto 0);

Q: out std_logic_vector (3 downto 0));

end CONTADOR;

architecture comportamento of CONTADOR is

signal CONT: std_logic_vector (3 downto 0);

begin

process (CLK)

begin

if (CLK’event and CLK = ‘1’) then

if (CLR = ‘1’) then CONT <= “0000”;

elsif (LOAD = ‘1’) then CONT <= D;

elsif (EN = ‘1’ and UP = ‘1’ and

CONT = “1001”) then

CONT <= “0000”;

elsif (EN = ‘1’ and UP = ‘1’) then

CONT <= CONT + “0001”;

elsif (EN = ‘1’ and UP = ‘0’ and

CONT = “0000”) then

CONT <= “1001”;

elsif (EN = ‘1’ and UP = ‘0’) then

CONT <= CONT - “0001”;

end if;

end if;

end process;

Q <= CONT;

end comportamento;

Esta arquitetura se refere a um contador do tipo

Provas

Considere o modelo de um sistema linear dado pela seguinte representação em espaço de estado:

\( \dot {X} (t) \, = \, \begin {bmatrix} -11 \,\,\,\,\,\,\, -60 \\ 1 \,\,\,\,\,\,\,\,\,\, 5 \end {bmatrix} \, X (t) \, + \, \begin {bmatrix} 1 \\ 0 \end {bmatrix} u (t) \, y(t) \, = \, [1 \,\, 15]X (t) \)

Os polos deste sistema são:

Provas

Considere o sistema de controle em malha fechada ilustrado na figura acima, onde K > 0 representa o ganho a ser ajustado no compensador. Pelo compensador adotado e levando-se em conta o diagrama do lugar das raízes (root locus) desse sistema, conclui-se que o sistema será

Provas

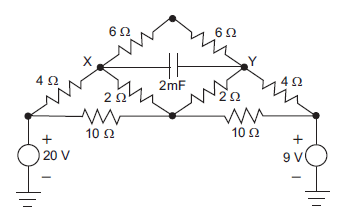

A figura acima apresenta um circuito elétrico com fontes de corrente contínua. O capacitor encontra-se operando em regime permanente. A ddp, em volts, entre os terminais X e Y do capacitor é, aproximadamente,

Provas

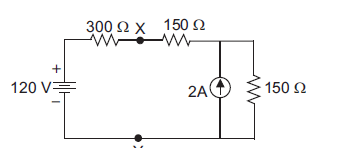

No circuito da figura acima, a tensão do Circuito Equivalente de Thevenin, dada em volts e calculada entre os pontos X e Y, é:

Provas

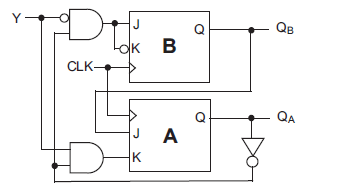

Quando o circuito ilustrado na figura acima estiver no estado QBQA = 00, com Y = 1, os flip-flops B e A executarão, respectivamente, as operações de

Provas

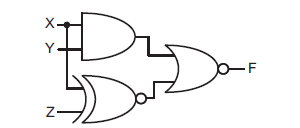

A figura acima ilustra o circuito digital que relaciona o sinal F com os sinais binários de entrada X, Y e Z. De acordo com o circuito, a expressão booleana mais simplificada de F em função de X, Y e Z é

Provas

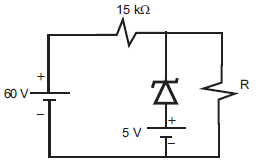

No circuito da figura acima, o Diodo Zener é considerado ideal e opera, em sua região ativa, com tensão nominal de 16 V.

Qual o valor do resistor R, em \( k \Omega \), para que a corrente no Zener seja de 2 mA?

Provas

Caderno Container