Foram encontradas 50 questões.

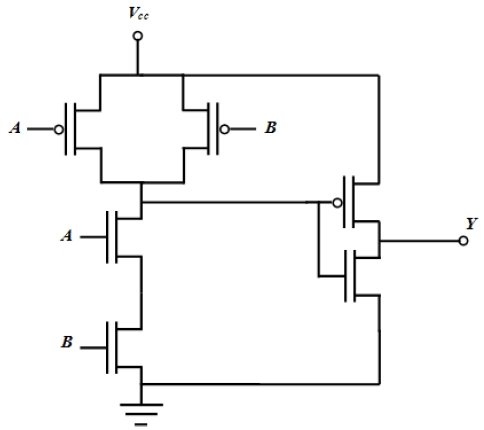

Observe o esquemático abaixo.

Considerando a lógica positiva (“0” lógico corresponde a 0 V e “1” lógico corresponde a Vcc), o esquemático acima em tecnologia CMOS, representa uma porta lógica

Provas

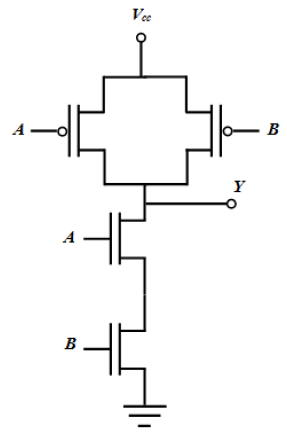

Observe o esquemático abaixo.

Considerando a lógica positiva (“0” lógico corresponde a 0 V e “1” lógico corresponde a Vcc), o esquemático acima em tecnologia CMOS, representa uma porta lógica

Provas

Observe o esquemático abaixo.

Considerando a lógica positiva (“0” lógico corresponde a 0 V e “1” lógico corresponde a Vcc), o esquemático acima em tecnologia CMOS, representa uma porta lógica

Provas

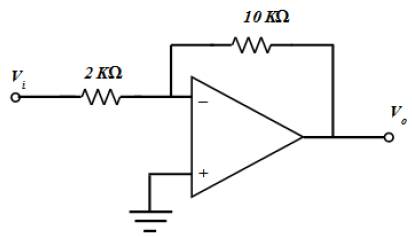

Observe a figura abaixo.

O ganho em malha fechada para o circuito esquematizado na figura acima é

Provas

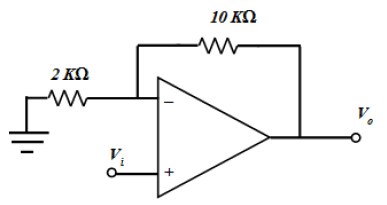

Observe a figura abaixo.

O ganho em malha fechada para o circuito esquematizado na figura acima é

Provas

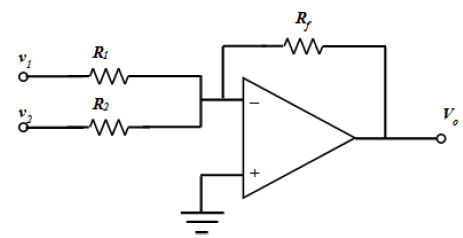

Observe o esquemático abaixo.

No esquemático acima, os valores de R1 e R2, de modo a se obter Vo = -(2v1 + 3v2), são

Provas

Um transistor NMOS tipo enriquecimento, operando na região de saturação, com VT = 0,7 V, tem seu terminal de fonte (Source) aterrado e uma tensão de 1,5 Vdc aplicada ao terminal da porta (Gate). Considerando, ainda, \( \mu_n \)Cox = 80 \( \mu \)A/V2, largura do canal igual a 35 \( \mu \)m e comprimento do canal igual a 3,5 \( \mu \)m, o valor da corrente de dreno é

Provas

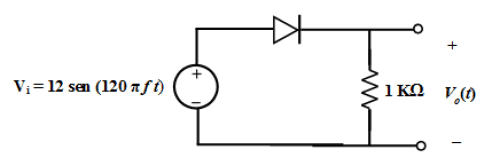

O circuito retificador de meia onda mostrado, esquematicamente, na figura abaixo, utiliza diodo de silício com queda de 0,7 V para qualquer valor de corrente.

O valor mais aproximado da tensão de pico na saída retificada é

Provas

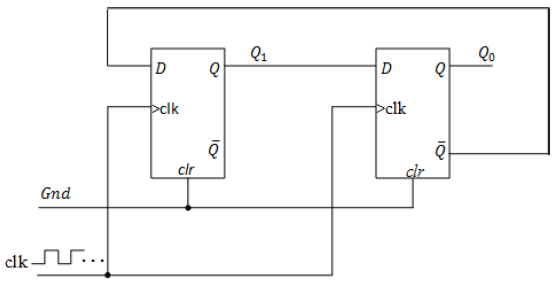

Considere o esquemático mostrado na figura abaixo.

Supondo que inicialmente os dois flip-flops estejam re-setados, a sequência de valores nas saídas Q1Q0 é, respectivamente,

Provas

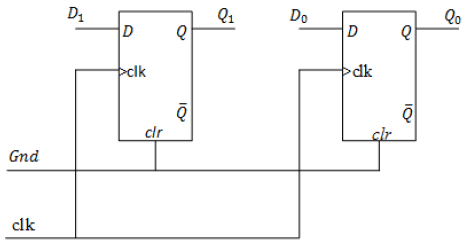

O esquemático abaixo representa um contador binário crescente de módulo 4. O flip-flop mais a esquerda representa o bit mais significativo.

Supondo que no estado inicial os flip-flops estão re-setados, as equações para as entradas D1 e D0 devem ser escritas como

Provas

Caderno Container