Foram encontradas 20.519 questões.

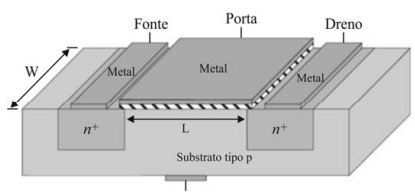

Considerando a figura precedente, que ilustra a geometria de uma porta do tipo MOS, julgue o item a seguir.

Na ilustração, a dimensão identificada por W corresponde à largura do canal do MOSFET.

Provas

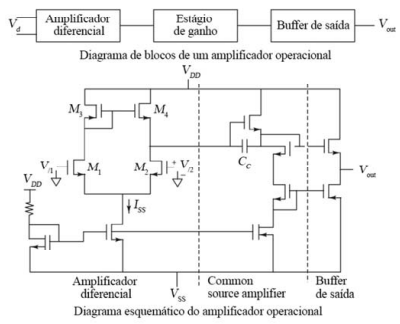

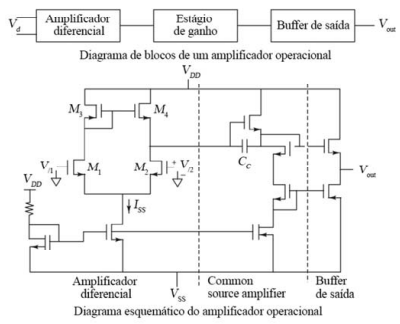

No processo de design de um amplificador operacional CMOS, a seleção do tamanho dos dispositivos MOSFET e das correntes de polarização tem influência direta em parâmetros tais como ganho, CMRR, dissipação de potência, ruído e taxa de variação (slew rate). Esse processo é iterativo e requer ajustes baseados em simulações, em que aumentar o tamanho dos MOSFETs (aumentando W) com uma menor VGS (tensão entre porta e fonte) pode melhorar o emparelhamento, aumentar o ganho e reduzir o ruído, porém, podendo resultar em uma área de layout maior e potencialmente em menor velocidade de operação.

Provas

No amplificador operacional CMOS mostrado, o amplificador diferencial deve fornecer a maior parte do ganho do sistema, enquanto o estágio de ganho em fonte comum serve principalmente para prover a compensação de frequência necessária; o buffer de saída é utilizado para equalizar as tensões de entrada diferencial sem amplificar o sinal.

Provas

Em relação a circuitos integrados em larga escala de fabricação (VLSI), julgue o item que se segue.

Nos circuitos CMOS, devido à diferença de mobilidade entre lacunas e elétrons em materiais semicondutores, os transistores NMOS usados em circuitos digitais têm aproximadamente o dobro do tamanho dos transistores PMOS.

Provas

Em relação a circuitos integrados em larga escala de fabricação (VLSI), julgue o item que se segue.

Em materiais semicondutores fabricados com silício, a mobilidade de elétrons é maior que a mobilidade das lacunas, por isso, na fabricação de circuitos de alto desempenho e baixo consumo, é empregada, predominantemente, a tecnologia que utiliza apenas transistores NMOS.

Provas

Em relação a circuitos integrados em larga escala de fabricação (VLSI), julgue o item que se segue.

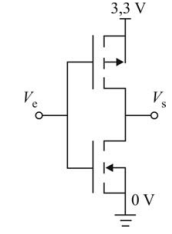

O diagrama a seguir ilustra uma configuração compatível com uma porta lógica inversora CMOS, com a entrada representada por Ve e a saída, pela tensão Vs.

Provas

Em relação a circuitos integrados em larga escala de fabricação (VLSI), julgue o item que se segue.

O diagrama a seguir ilustra uma configuração compatível com uma porta lógica NOR CMOS, com as entradas representadas por VA e VB a saída, pela tensão VS.

Provas

A técnica de corrosão úmida possui uma vantagem com relação à corrosão a seco, pois é um processo isotrópico, que atua uniformemente em todas as direções.

Provas

Acerca das técnicas de deposição de filmes finos, julgue o item subsequente.

As técnicas de deposição para filmes finos podem ser classificadas em deposição física de vapor (PVD) e deposição química de vapor (CVD).

Provas

Acerca das técnicas de deposição de filmes finos, julgue o item subsequente.

A pulverização catódica (sputtering) é um processo de deposição química de vapor (CVD) através de evaporação térmica.

Provas

Caderno Container