Foram encontradas 20.456 questões.

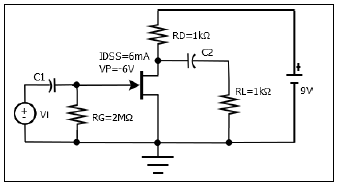

Com base no amplificador apresentado abaixo, o valor quiescente (VDSQ) da tensão entre dreno e fonte é, em V, de:

Provas

Questão presente nas seguintes provas

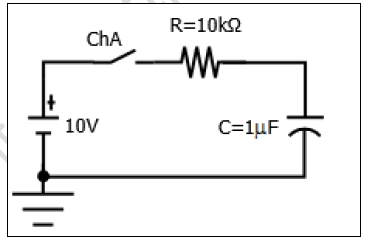

Observe o circuito a seguir.

Considerando o capacitor descarregado, o valor da tensão sobre o resistor, 5 segundos depois que a chave ChA for fechada, será, em V, de:

Provas

Questão presente nas seguintes provas

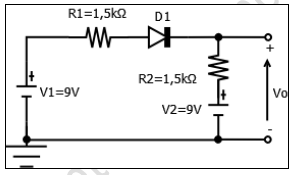

Observe o circuito abaixo.

Considerando D1 um diodo de silício, o valor de Vo para o circuito, em V, é de:

Provas

Questão presente nas seguintes provas

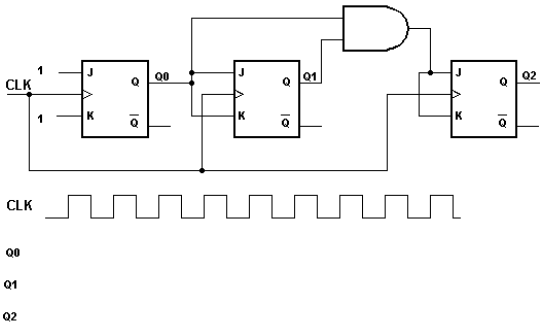

Observe o contador formado por três flip-flops JK e uma porta AND. As entradas J e K do flip-flop cuja saída é Q0 estão permanentemente conectadas em um nível lógico 1.

O módulo desse contador é:

Provas

Questão presente nas seguintes provas

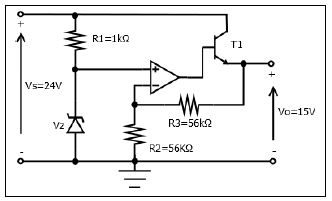

A tensão de entrada não regulada (Vs) do circuito a seguir é de 24V.

Nesse caso, para que a tensão de saída regulada (Vo) seja de 15V, a tensão de referência (Vz) do diodo zener, em volts (V), deve ser:

Provas

Questão presente nas seguintes provas

Um técnico em eletrônica precisa verificar o funcionamento de um conversor D/A com saída em tensão. A resolução indicada no manual do conversor é de 5 mV e o conversor possui uma entrada digital de 4 bits, D3, D2, D1 e D0, sendo D3 o bit mais significativo, e essas entradas compatíveis com a lógica TTL. O técnico faz a verificação e percebe que o conversor não está apresentando o comportamento esperado, como mostra a tabela abaixo.

| Entrada Digital | Saída | ||||||

| D3 | D2 | D1 | D0 | Vo (mV) | |||

| 0 | 0 | 0 | 0 | 0 | |||

| 0 | 0 | 0 | 1 | 5 | |||

| 0 | 0 | 1 | 0 | 10 | |||

| 0 | 0 | 1 | 1 | 15 | |||

| 0 | 1 | 0 | 0 | 0 | |||

| 0 | 1 | 0 | 1 | 5 | |||

| 0 | 1 | 1 | 0 | 10 | |||

| 0 | 1 | 1 | 1 | 15 | |||

| 1 | 0 | 0 | 0 | 40 | |||

| 1 | 0 | 0 | 1 | 45 | |||

| 1 | 0 | 1 | 0 | 50 | |||

| 1 | 0 | 1 | 1 | 55 | |||

| 1 | 1 | 0 | 0 | 40 | |||

| 1 | 1 | 0 | 1 | 45 | |||

| 1 | 1 | 1 | 0 | 50 | |||

| 1 | 1 | 1 | 1 | 55 | |||

Com base nas informações identificadas, a possível causa do mau funcionamento do conversor D/A é:

Provas

Questão presente nas seguintes provas

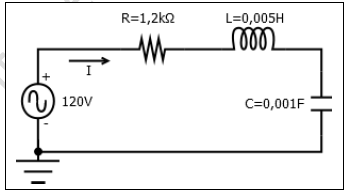

Observe o circuito abaixo:

Considerando que a frequência do sinal aplicado corresponde à frequência de ressonância do circuito, o valor da corrente I, em mA, é igual a:

Provas

Questão presente nas seguintes provas

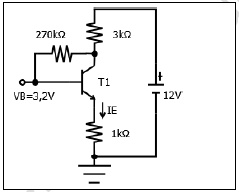

No circuito abaixo, sabendo que a tensão na base (VB) é 3,2V, o valor da corrente de emissor (IE), em miliampère (mA), é igual a:

Provas

Questão presente nas seguintes provas

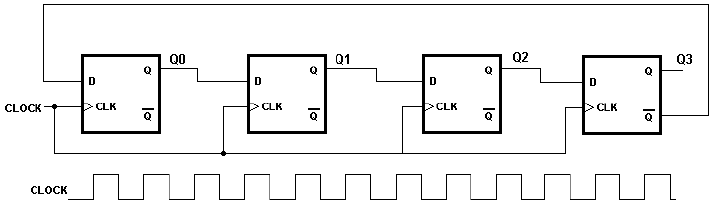

Quatro flip-flops do tipo D estão interligados conforme o diagrama apresentado abaixo. Considere a frequência do sinal de CLOCK de 40 kHz e o estado inicial dos flip-flops, sendo Q0=Q1=Q2=Q3=0.

As frequências dos sinais Q0, Q1, Q2 e Q3 são, em kHz, respectivamente, iguais a:

Provas

Questão presente nas seguintes provas

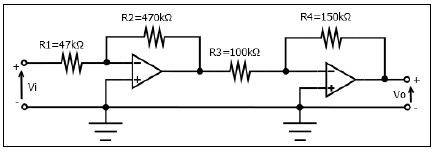

Observe o circuito abaixo:

O valor do ganho de tensão do circuito, !$ { \Large {Vo \over Vi}} !$, corresponde a:

Provas

Questão presente nas seguintes provas

Cadernos

Caderno Container