Foram encontradas 12.749 questões.

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FGV

Orgão: INPE

Diante do exposto, assinale a opção que melhor descreve um aspecto da arquitetura escalar de computadores.

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FGV

Orgão: INPE

Relacione as arquiteturas de computadores às suas características.

1. Von Neumann

2. Harvard

( ) Utiliza barramentos distintos para dados e instruções.

( ) O processador busca e executa uma instrução por vez, em sequência.

( ) Utiliza barramentos compartilhados para dados e instruções.

( ) As instruções e os dados são armazenados na mesma memória.

( ) Armazena dados e instruções em memórias distintas

Assinale a opção que indica a relação correta, segundo a ordem apresentada.

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FGV

Orgão: INPE

I. No método big-endian, o endereçamento inicia pelo byte menos significativo.

II. O acesso aos bytes de palavras armazenadas na memória independe do método de ligação (big-endian ou little-endian) para processadores de menos de 32 bits.

III. Em ambos os métodos de ligação (big-endian e little-endian), os bits menos significativos do barramento de dados estão ligados aos bits menos significativos da palavra armazenada na memória.

Está correto o que se afirma em

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FGV

Orgão: INPE

Suponha que as palavras 25 38 94 67H (identificada por P1) e 18 31 72 46H (identificada por P2) estão armazenadas a partir dos endereços 0010H e 002CH, respectivamente.

Nesse contexto, analise as afirmativas a seguir.

I. A leitura do endereço 0014H retorna o byte 38H da palavra P1.

II. A leitura do endereço 002FH retorna o byte 46H da palavra P2.

III. Entre as palavras P1 e P2 podem ser armazenadas doze palavras.

Está correto o que se afirma em

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FGV

Orgão: INPE

Os processadores com arquitetura

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FGV

Orgão: INPE

Sobre este tipo de memória, analise as afirmativas a seguir.

I. A memória cache de menor nível (L1) é a que possui o maior tempo de acesso.

II. Os dados armazenados na memória cache de nível L1 são mais frequentemente acessados que aqueles no nível L3.

III. O tempo de acesso à memória cache não influencia o desempenho do processador.

Está correto o que se afirma em

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FGV

Orgão: INPE

- ProcessadoresComponentesALU: Arithmetic Logic Unit

- ProcessadoresCiclo de InstruçãoFases do Ciclo de Instrução

A tarefa de acessar a memória principal em busca de instruções é efetuada pela(o)

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FGV

Orgão: INPE

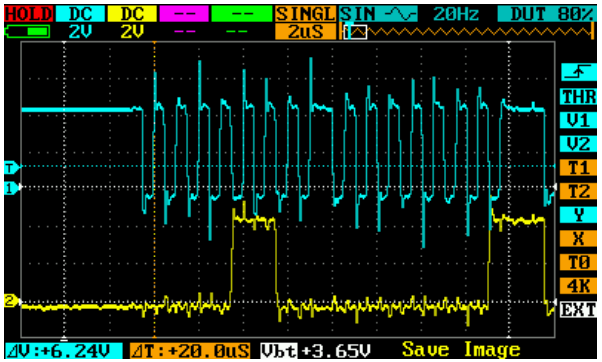

Fonte: Módulos e Sensores: Guia de Interface com o Arduino. Editora Interciência.

Sabe-se que a amostragem é no flanco de subida do relógio. Os dois bytes comunicados, em hexadecimal, são

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FGV

Orgão: INPE

Assinale a opção que indica o primeiro byte gerado, em binário.

Provas

Disciplina: TI - Organização e Arquitetura dos Computadores

Banca: FGV

Orgão: INPE

Texto I

Os Processadores Digitais de Sinais (DSPs) são componentes fundamentais presentes em uma ampla gama de aplicações, abrangendo desde sistemas de comunicações sem fio e processamento de áudio até aplicações em imagens médicas e automotivas. Eles são projetados especificamente para manipular sinais digitais em tempo real, oferecendo capacidades de processamento eficientes e otimizadas para tarefas como filtragem, modulação, demodulação e análise de sinais.

A seguir, é apresentada uma lista comparativa entre cinco processadores de arquiteturas semelhantes, na qual são fornecidas informações sobre a faixa de frequência de operação do DSP, o número de MIPS (milhões de instruções por segundo) por MHz (frequência de operação do DSP) e a potência por instrução MIPS.

- DSP-P1: 300-750 Mhz; 3 MIPS/MHz; 0,15 mW/MIPS

- DSP-P2: 500-600 Mhz; 6 MIPS/MHz; 0,30 mW /MIPS.

- DSP-P3: 200-300 Mhz; 5 MIPS/MHz; 0,10 mW/MIPS.

- DSP-P4: 160-400 Mhz; 2 MIPS/MHz; 0,20 mW/MIPS.

- DSP-P5: 300-900 Mhz; 8 MIPS/MHz; 0,25 mW/MIPS.

Obs.: Considere que o número de instruções e a potência por MHz permanecem inalterados dentro da faixa de operação de frequências de cada processador.

Deseja-se empregar um determinado DSP para filtragem de um sinal, cujas características exigem que o referido DSP possua uma capacidade de processamento de no mínimo 3000 MIPS. Os DSPs capazes de implementar o filtro supracitado são

Provas

Caderno Container