Foram encontradas 20.584 questões.

O uso de Controladores Lógicos Programáveis é de grande importância para acionamentos de equipamentos no âmbito mundial. Além da importância econômica em virtude das facilidades e funcionalidades, destaca-se, também, a questão da segurança para fazer certos acionamentos. Um dos sistemas de segurança utilizados é o intertravamento. Com essa técnica alguns equipamentos têm seus ligamentos impossibilitados devido à utilização de outros equipamentos.

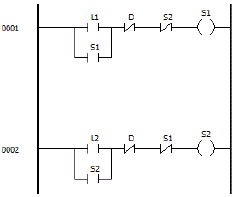

Com base no sistema de acionamento em linguagem Ladder, mostrado a seguir, podemos afirmar que:

Provas

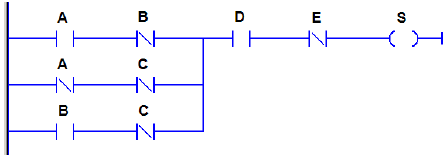

Uma das linguagens gráficas mais utilizadas para realizar a programação de Controladores Lógicos Programáveis (CLPs) é o diagrama Ladder; um exemplo para este diagrama pode ser observado na figura a seguir:

Para o diagrama Ladder apresentado, utilize a álgebra de Boole para determinar a equação lógica da programação.

Provas

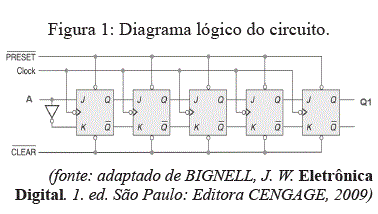

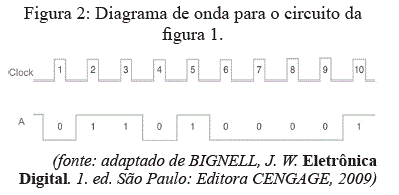

Considerando o circuito e o diagrama de onda abaixo:

Supondo que no circuito da figura 1 todos os flip-

-flops estejam inicialmente com o valor lógico de suas saídas Q em nível lógico baixo, que a entrada

A assuma o valor correspondente ao diagrama de

onda da figura 2, e as entradas ![]() e

e ![]() estejam sempre em nível lógico alto, quantos pulsos

de Clock serão necessários para que a saída Q1

tenha nível lógico alto?

estejam sempre em nível lógico alto, quantos pulsos

de Clock serão necessários para que a saída Q1

tenha nível lógico alto?

Provas

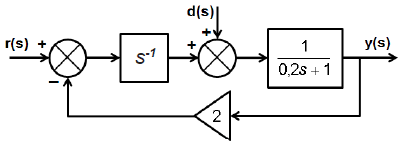

Para um determinado sistema de controle, considere o seguinte diagrama de blocos:

Onde y(s) é a variável de processo controlada, d(s) é um sinal de distúrbio, r(s) é a referência do sistema (setpoint), e s é o operador de Laplace.

Assinale a alternativa que apresenta as funções de transferência !$ y(s)/d(s) !$ e !$ y(s)/r(s) !$ correta:

Provas

Disciplina: Engenharia Eletrônica

Banca: Consulplan

Orgão: Pref. Formiga-MG

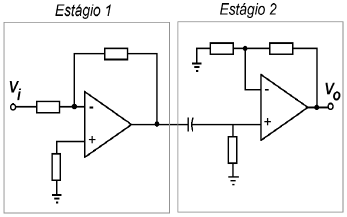

O circuito é composto dos estágios 1 e 2 em série, cada um utilizando um amplificador operacional configurado respectivamente como:

Provas

Disciplina: Engenharia Eletrônica

Banca: Consulplan

Orgão: Pref. Formiga-MG

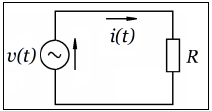

O circuito é alimentado por uma tensão v(t) = 30 sen !$ ωt !$ (V), onde !$ ω !$ = 628 rad/s, sendo R puramente resistivo de valor 15 !$ Ω !$.

De acordo com o circuito apresentado, analise as afirmativas a seguir.

I. A corrente i(t) = 450 sen !$ ωt !$ (A).

II. A potência instantânea p(i) = 60 sen2 !$ ωt !$ (W).

III. A frequência da fonte é de aproximadamente 100 Hz.

Está(ão) correta(s) apenas a(s) afirmativa(s)

Provas

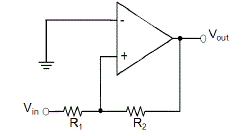

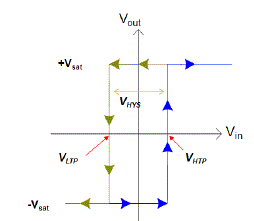

Em aplicações práticas, é muito comum observar em sistemas eletrônicos para automação a presença de ruído nos sinais oriundos de sensores ou transdutores. Em um circuito comparador comum, por exemplo, este ruído pode levar ao chaveamento indesejado de algum atuador. Uma forma de reduzir os efeitos oriundos do ruído é a utilização de um circuito comparador com histerese não-inversor, o qual é muito conhecido como circuito Schmitt Trigger (ST). A figura a seguir ilustra o ST:

A figura a seguir ilustra o ST:

Onde Vout é o sinal de saída do circuito comparador, Vin é o sinal de entrada, Vsat é a tensão de saturação do circuito, VHYS é a banda de histerese, VLTP é o limite inferior para comutação e VHTP é o limite superior.

Considerando o circuito apresentado acima, dado que Vsat = 12V, R2 = 10k?, R1 = 3k?, e Vin = 1,5V, qual o valor para a banda de histerese VHYS?

Provas

Os microcontroladores da família PIC18F, podem possuir PULL-UP’s internos em seus pinos de IO.

Ao utilizar um pino de IO, que possui PULL-UP interno, como OUTPUT, é necessário:

Provas

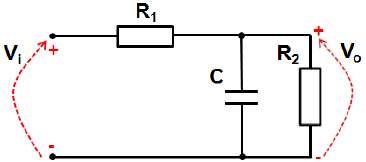

Seja um circuito elétrico representado pelo diagrama da figura abaixo:

Onde: Vi é o sinal de entrada do circuito, Vo é o sinal de saída, R1 e R2 são resistores, e C é um capacitor.

Para o circuito dado, qual a função de transferência !$ G(s) = V_o(s)/V_1(s) !$ que modela o sistema dinâmico?

Provas

A seguir apresenta-se um código em VHDL. Esta linguagem é muito utilizada para descrever hardwares, e também para configurar dispositivos eletrônicos baseados em FPGA.

|

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY BLOG IS PORT ( Op : IN STD_LOGIC_VECTOR (2 DOWNTO 0); A,B : IN STD_LOGIC_VECTOR (7 DOWNTO 0); R : OUT STD_LOGIC_VECTOR (7 DOWNTO 0)); END BLOG; ARCHITECTURE COMP OF BLOG IS BEGIN P1 : PROCESS (Op,A,B) BEGIN CASE Op IS WHEN "001" => R <= A + B; WHEN "010" => R <= A - B; WHEN "011" => R <= A OR B; WHEN "100" => R <= A AND B; WHEN "101" => R <= A XOR B; WHEN "110" => R <= NOT(A); WHEN "111" => R <= "00000000"; WHEN OTHERS => R <= "11111111"; END CASE; END PROCESS P1; END COMP; |

A respeito do código em VHDL apresentado, é CORRETO afirmar que:

Provas

Caderno Container